cadence SPB17.4 - orcad - 层次原理图

时间:2022-09-11 00:30:00

cadence SPB17.4 - orcad - 层次原理图

前言

层次原理图的优点:

-

不要画大图(所有的电路都挤在一起,看不清楚,要来回缩放; 第三方参考工程的一部分子电路也很方便,不需要脱敏), 在一张子图中将局部电路(或在顶层原理图中将子图模块之间的接口关系)看的很清楚,从顶层原理图到子图(或从子图回到顶层原理图)很方便。

-

层次原理图层次原理图的子图,可以理清顶层总图与子图的电气接口连接关系。

-

如果需要迭代,当接口不变时,只需要改对应的子原理图就行。不要担心影响其他子电路(每张子图的网络标号不同(e.g. 子图A的GND为GND_A, 子图B的GND为GND_B, 2个子图的GND_X顶层原理图实际上是通过接口显示的, 在顶层电路图中, 实际上连接,实际上是一个网络), 与他人合作时不要担心引入对方的错误。

-

如果子图界面规划得很好,如果想把子图做成板子,也很方便. e.g. 将MCU做一个子电路MCU核心板.

当多张子图中有相同的网络标号名称时, DRC会报错:)

笔记

花了9周(约 9 x 7 天, 通过学习和实验解决问题)AD完全转到了cadence。

一开始, 画层次原理图, 临时笔记, 但不确定是否正确。

现在, 整个过程(从绘制原理图到制作板厂文件)都通过了,可以确认层次原理图的正确性。

用了一个星期,画了一张板子的原理图,画得很漂亮,看图也很方便。SPB17.4的DRC检查,报错太多。正在解决一个错误,一个错误。感觉就是记录下来。

记录画层原理图中的细节,都是分散的知识点。

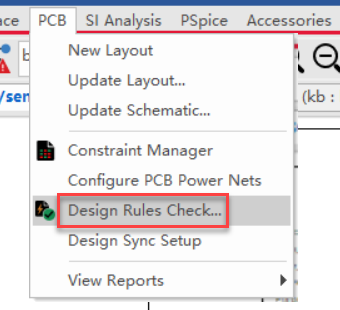

DRC检查设置

画层次原理图前, 先将DRC检查设置好.这是第一步,否则很多错误都找不到.后面都白用功了

画完层次原理图后,我觉得很漂亮,浏览电路模块也很方便。

但原理图的细节不一定正确。

这时要靠orcad SPB17.4自带原理图DRC检查是否正确。

经过原理图DRC检查, DRC全部通过后, 后续操作(e.g. 导出网表, PCB导入网表,放置元件)不会出错.

这突出了原理图的制作DRC的重要作用.

DRC选项能检查的选项,钩要都打上。只有自己能确认的选项才关掉. (e.g. 导致不必要的原理图DRC检查错误)

下面是我通过的一切DRC测试工程的检查SCH DRC选项. 基本都勾上了,去掉的选项已经测试过了.

最终目标:原理图完全正确, DRC完全通过(0错误,0警告).

Options

Rules Setup

Report Setup

ERC Matrix

这里使用的选项是默认的, 若此处改过,按Restore Defaults恢复按钮.

Exception Setup

不需要添加异常设置

工程设置好DRC选项后, 每次手动检查后,直接点击Run,开始检查。

绘制层次原理图的基本步骤

绘制方法

自顶向下画.

若要将现有的普通平面原理图转换为层次原理图, 遵循自上而下的方法, 快速改造.

元素

层次原理图比普通原理图多出5个元素如下, 其他绘画方法(从图纸接口连接到电气连接后)与普通原理图相同.

可用于子图和顶图的元素

Bus : 总线

Bus Entry : 总线入口

子图符号块中的元素:

Hierarchical Block : 子图符号块

Hierarchical Pin : 子图界面引脚

子图中的元素:

Hierarchical Port : 子图符号端口

例子

放置子图符号块

首先在顶层图纸上放置符号块

指定子图名称,按OK按钮.

按下鼠标左键, 拖出矩形,松开鼠标左键, 子图符号块就放好了.

双击图符号块, 让我们给定子图命名,然后按下OK按钮.

此时进入子图

从子图回到顶层图

右击子图中的菜单, 选择Ascend Hierarchy回顶层图纸.

回到顶层图纸

现在子图符号和子图已经建立,然后从主图到子图,只需双击主图中的子图符号块即可直接进入子图.

在子图符号块中添加子图Pin

是子图pin, 不是子图端口. 子图pin放置在子图符号块中. 子图端口放在子图中.

只有选择子图符号块,才能选择子图符号块Place菜单中的子图pin条目变为可操作状态.

在弹出框中指定子图pin名称, 选择类型为Passive, 点击确定.

左击在子图符号中选择合适的位置

放好Port pin然后右击完成操作.

port pin 完成后,就可以从了port pin上引出电气连线, 标上网络符号, 与顶层图纸上的其他网络相连.

子图符号块从顶层图纸更新port pin 到子图

此时,我们没有在子图中添加这个port pin对应的port, 现在可以从顶层图纸更新这个port pin 到子图成为子图上的一个port.

向下更新完port pin 后, 子图自动进入.

可以看到子图左上角一个对应的对应port.

注意: 如果将子图手动放置pin, 子图port(没使用orcad提供的更新功能), 必须使子图pin和子图port是一种类型, 且和这个port pin 其他相连的网络port如果类型相同, 防止DRC报错.

手动添加子图port

我们上面用的自顶向下方法增加的子图pin, 子图在子图中同步生成port.

现在我们试着手动添加子图port, 顶层图纸反向更新, 成为子图符号块port pin.

我们在子图中同步放置和更新port一样类型的prot. 选择类型, 名称,点击OK.

左击选择图纸左上角的合适位置, 放好了port. 然后右击子图空白处,选择操作结束.

操作结束后port样子.

此时,我们想更新手工添加的子图port子图符号块在顶层图纸中.

子图不能更新port的,需要回到顶层图纸.

左击选择顶层图纸中的子图符号块,右击菜单,从下到上同步.

可以看出,我们选择的子图符号已经在子图中使用了port为子图符号块更新pin.

此时,从子图可以在顶层图纸中使用port拉出电气连接,标注网络标号.

子图中的子图port, 现在也可以连接电气连接,标记网络,正常使用.

需要注意的是:子图中的子图port名称可以和网络一样.

但是顶层图纸中的子图pin网络不能和子图pin名字一样,否则DRC报错.

剩下的操作和普通图纸画一样, 均在图纸(子图或顶图)中操作, 图纸边界都是port或port pin

画完后, 要进行完整DRC检查. 如果第一次画层次原理图,会报很多错误。.需要自己根据官方文档和自己的猜测实验来逐一解决, 直到DRC检查完全通过(0错误,0警告).

碎碎念

放大图纸

CTRL + 鼠标中键向上滚动,可以放大图纸。

为啥要先放大呢? 如果DRC检查结果有错误,双击出错条目后,会跳到报错点。如果图纸没放大,即使跳到报错点,也看不清是哪里报错。

跳转到DRC报错点

双击下面的报错条目, 会直接跳到报错点.

总线(bus)的使用

-

总线(bus)通常只能适合网络标号前缀一致,标号后缀增量加1的情况。

e.g. P0.0, P0.1, P0.2, … , P0.5, P0.6, P0.7 可以使用总线连接 -

如果网络标号不连续, 是不能作为bus连接的.

-

总线上必须放置bus网络标号(至少1个, 也可以放置多个(e.g. 在bus连接的2坨网络连接处都放bus网络标号))

e.g. 在总线连接的2断附近, 都标注上bus的网络标号为 P0[0…7]. 其实只要标注一个就行. 如果bus连线比较长,可以标注相同的bus标号多个. -

bus网络标号的格式

P0.[0…7] 或 P0[0:7]

但是在一条总线上, 格式只能是同一种, 否则报错.

连续的网络标号是指bus的一边是连续就行, e.g. 总的一处是P3.[0:3], 其他处是 P3.2, P3.3, 还有一处是P3.1, P3.0

如下所示:

-

Bus Entry是没法设置什么信息的,只是用来连接wire和bus.

wire是没法直接连入bus的, 必须借助 Bus Entry。 -

Bus Entry连接的wire上,必须放置网络标号。

-

如果使用了子图和子图端口(Hierarchical Port, Hierarchical Pin), 必须保证

Hierarchical Port 名称是全局(所有子图和顶层图)唯一的.Hierarchical Port 和 Hierarchical Pin 的名称必须是一样的.

但是Hierarchical Pin连出的电气连线上的网络名称,必须是和Hierarchical Pin名称不一样.

e.g. Hierarchical Pin 的名称是 GND_SUB_PAGE1, 那么顶层图纸上从 GND_SUB_PAGE1 pin引出的网络必须是其他名称 e.g. GND.

否则DRC检查报错。

Hierarchical Port 只是代表子图符号和总图的连接点(接口),名字是啥都没事(只要保证和其他子图端口不重名),因为起决定作用的是网络标号。只有网络标号才代表真正的电气连接关系

Hierarchical Port 必须是唯一的名称. 否则DRC报错.

Hierarchical Port 在子图符号块(Hierarchical Block)中叫做 Hierarchical Pin

Hierarchical Port 在具体子图中叫Hierarchical Port.

Hierarchical Port 和 Hierarchical Pin 代表的是同一样东西,只是位置不一样。

PCB上的对应网络名称

等画好PCB, PCB和原理图上的网络名称对应关系:

-

如果是未命名的网络, PCB上用的是原理图产生网表时,自动产生的网络名称.

-

如果是子图上未经过接口的显势命名的网络名称, 和PCB上的网络名称相同.

-

如果是子图上经过接口的网络名称, 最终的网络名称是由顶层图纸的接口之间连线上的手工命令的网络名称决定.

就是说, 顶层原理图的网络标号优先于子图的网络标号. e.g. 子图A的GND_A经过接口到顶层图纸, 子图B的GND_B经过接口到顶层图纸, 在顶层接口用电气线连接后, 标注网络为GND. 那么PCB上显示的网络名称为GND.

高亮bus或单个网络名称的网络连接

查看或排错时, 有高亮网络或bus的需求.

选中电气连线(bus或wire), 右击选择Select Entire Net

高亮后, 整个网络就被点亮了.

离图连接器

层次原理图分2种:

-

一种是上面这种自顶向下方式的层次原理图, 从顶层原理图开始看图,双击子图符号,会跳到子图.

从子图也可以方便的从右键菜单上回到顶层图纸.

-

还有一种方式, 是不带子图符号块的层次原理图.

在同一个原理图文件夹节点下,右击菜单

New Page建立一系列平行的图纸, 这些图纸没有主次之分.每张图纸之间通过离图连接器作为接口连接.

这种没有上下级关系的层次原理图, 失去了软件辅助进行子图/主图互相切换的功能. 我没有采用这种层次原理图.

但是看ST这样的大厂给的demo板子原理图, 大部分还是采用了离图连接器这种层次原理图.

感觉使用离图连接器的层次原理图没有使用子图符号块的原理图方便.

END

因为不确认层次原理图画的是否正确, 等到全部流程(画原理图, PCB, 出制板厂文件)都走通了, 才做的层次原理图的正式总结.

第一次画层次原理图, 全部画完了, 才做的DRC, 好多错误, 排查了好久.

中间出的那些DRC错误,除了封装没填之外, 都不记得是啥了, 只记得自己用了很久, 才将那些DRC都消掉了.

结论 : 如果自己再用cadence SPB17.4 的 orcad capture and cis 画层次原理图, 是没有任何问题的.

补充 - 2022_0622_0910

和CSDN的同学讨论问题, 他的建议如下

感觉用offpage链接还是直观点吧,毕竟现在都是能用网络名就用网络名代替

我倾向采用port, 理由如下:

-

大厂出的图纸, 一般是使用离图连接器的.

但是使用离图连接器的层次原理图是平面的, 子图之间没有主次关系,失去了图纸之间的关系辅助(主图切到子图, 子图回到主图). -

如果是打印出来给第三方的图, 2种原理图都可以, 感觉差别不大.

-

如果是设计文件.dsn给自己或第三方用, 用port连接的有主次关系的层次原理图还是方便一些.

总结: 是否使用层次原理图? 是否使用平面型的层次原理图? 或使用port作为接口的层次原理图? 都可以, 看个人习惯. 不是多大的事, 不影响画原理图图/出网表/做板子.