PCIe 均衡技术介绍(逻辑物理篇)

时间:2022-09-09 03:00:00

??点击查看选择 PCIe 系列文章??

??点击进入芯片设计验证社区查看更多精彩内容??

???声明:

- ?? 作者主页:【MangoPapa的CSDN主页】。

- ?? 本文首发于CSDN,请注明转载或引用的来源 https://mangopapa.blog.csdn.net/article/details/124539607。

- ?? 本文的目的是非盈利性质 个人学习记录 及 知识分享。由于个人能力有限,协议解释可能不正确。如果您参考本文进行产品设计或其他事项并造成不良后果,我不承担相关法律责任。

- ?? 本文使用的图片或相关引用侵犯了您的合法权益,请联系我删除。

- ?? 欢迎指出文章的错误,欢迎与我交流 ~

- ?? 邮箱:mangopapa@yeah.net

引言

??近期学习了 PCIe 平衡相关事项,查阅无数文件。闲着,整理一下,供个人随时查阅,也供他人参考。PCIe 平衡系列文章分为 3 篇:

- PCIe 均衡技术介绍(总结) ,简要介绍平衡概念、信号补偿技术和平衡系数协商过程,初步了解 PCIe 平衡可以读这篇文章。

- PCIe 均衡技术介绍(电气物理篇) ,从电气物理层面介绍平衡器的相关技术细节和平衡参数测量和评价方法 PCIe 本文可以阅读平衡底层原理。

- PCIe 均衡技术介绍(逻辑物理),从逻辑物理层面介绍平衡系数协商的过程和与平衡相关的协议标准,想深入学习 PCIe 本文可参考均衡系数协商过程。

??已包含本系列 PCIe 2.5 GT/s、5 GT/s、8 GT/s、16 GT/s、32 GT/s 相关均衡介绍尚未整理 64 GT/s 相关平衡的介绍还没有整理出接收端压力眼图的测试部分。本文的技术水平和能源投入有限。可以想象,这篇文章有很多错误。我希望读者能指出,谢谢!

??点击获取完整性 pdf 文档 ?? https://mp.weixin.qq.com/s/8RmTb-gsLntUllteeKE6-g

文章目录

- 引言

- 1. PCIe 均衡技术介绍(总结)

- 2. PCIe 均衡技术介绍(电气物理)

- 3. PCIe 均衡技术介绍(逻辑物理)

-

- 3.1 PCIe 均衡机制

-

- 3.1.1 两种平衡机制

-

- 3.1.1.1 自动平衡机制

-

- 3.1.1.1.1 自动均衡中的 DLLP Blocking

- 3.1.1.2 软件平衡机制

- 3.1.2 平衡加速和关闭

-

- 3.1.2.1 Equalization bypass to highest rate

- 3.1.2.2 No equalization needed

- 3.1.3 判断和措施均衡结果

-

- 3.1.3.1 平衡成功的标志

- 3.1.3.2 重新平衡机制

-

- 3.1.3.2.1 何时重新 EQ ?

-

- 3.1.3.2.1.1 均衡失败

- 3.1.3.2.1.2 平衡设置问题

- 3.1.3.2.1.3 改变链路宽度

- 3.1.3.2.2 重新 EQ 过程

-

- 3.1.3.2.2.1 DSP 请求重新 EQ

- 3.1.3.2.2.2 USP 请求重新 EQ

- 3.1.3.2.2.3 Quiesce Guarantee 机制

- 3.1.3.2.2.4 Perform Equalization 与 Link Equalization Request 有何区别?

- 3.1.4 在不同的情况下 EQ 需求

-

- 3.1.4.1 切速中的 EQ

-

- 3.1.4.1.1 2.5 GT/s -> 8 GT/s 或 5 GT/s -> 8 GT/s

- 3.1.4.1.2 8 GT/s -> 16 GT/s 或 16 GT/s -> 32 GT/s

- 3.1.4.1.3 2.5 GT/s -> 32 GT/s 或 5 GT/s -> 32 GT/s

- 3.1.4.1.4 跳转速度相同 EQ

- 3.1.4.2 Crosslink 中的 EQ

- 3.1.4.3 Loopback 或 Compliance 中的 EQ

- 3.2 PCIe 协商均衡系数

-

- 3.2.1 DSP

-

- 3.2.1.1 Phase 1

- 3.2.1.2 Phase 2

- 3.2.1.3 Phase 3

- 3.2.2 USP

-

- 3.2.2.1 Phase 0

- 3.2.2.2 Phase 1

- 3.2.2.3 Phase 2

- 3.2.2.4 Phase 3

- 3.2.3 Preset 及 Coefficient 响应

- 3.2.4 start_equalization_w_preset

- 3.3 EQ 举例

-

- 3.3.1 速率 8 GT/s Equalization Flow

- 3.3.2 速率 16 GT/s Equalization Flow

- 3.3.3 Equalization Bypass Flow

- 参考

1. PCIe 均衡技术介绍(总结)

链接:PCIe 均衡技术介绍(总结)

2. PCIe 均衡技术介绍(电气物理)

链接: PCIe 均衡技术介绍(电气物理篇)

3. PCIe 均衡技术介绍(逻辑物理篇)

除非特别说明了无需 EQ,在初次切速到 8 GT/s 或以上速率时,必须进行 EQ。在不降低链路可靠性的情况下,EQ 完成之后 Rx 依然可以精调其参数。

3.1 PCIe 均衡机制

3.1.1 两种均衡机制

PCIe 协议定义了两种均衡机制:自动均衡与软件均衡机制,接下来分别介绍这两种均衡机制。

3.1.1.1 自动均衡机制

自动均衡机制是指在没有外部软件控制的情况下,PCIe 链路两端设备自主发起的均衡过程。若链路两端设备都支持 8 GT/s 或以上速率,则可以调用自动均衡机制。协议不建议自动均衡与软件均衡混合使用的方式,比如 8 GT/s 及 16 GT/s 时采用自动均衡,到 32 GT/s 时又改用软件均衡,但协议中也未禁止这种操作。

采用自动均衡机制时,Tx & Rx 每一条 Lane 针对每一种要做 EQ 的速率都做了调整。链路训练进入 L0 状态后,如果 PCIe 设备知道 EQ 未完成、其接下来要进行 EQ,无论当前速率是多少(即便已经达到目标速率),双方都不能发送任何 DLLP。

3.1.1.1.1 自动均衡中的 DLLP Blocking

对于采用自动均衡机制的 PCIe 设备,USP 在收到 DSP 发来的 DLLP 之前不能发送任何 DLLP;DSP 在 EQ 完成之前也不能发送任何 DLLP。

对于采用自动+软件混合均衡机制的 PCIe 设备,若双方设备均支持 16 GT/s 或更高速率,且 DSP 仅在 8 GT/s 时采用自动均衡机制,则 DSP 仅在 8 GT/s 速率 EQ 完成前禁止发送 DLLP,16 GT/s 及更高速率时不必遵循此规则。若双方设备均支持 32 GT/s 或更高速率,且 DSP 仅在16 GT/s时采用自动均衡机制,则 DSP 在完成 16 GT/s 速率 EQ 前禁止发送 DLLP,完成 8 GT/s EQ 前同样禁止,32 GT/s 及更高速率时不必遵循此规则。

若由于 DLLP Blocking 导致设备从 L0 延迟进入 Recovery,USP 或 DSP 端有可能会发生推测电气闲超时或 DLLP 超时,这两种超时均是不可报告的错误。当发生上述两种超时时,链路会进入 Recovery 重新对链路进行训练,不会影响正确的链接操作。

3.1.1.2 软件均衡机制

软件均衡机制是指 PCIe 设备在外部软件控制下发起的均衡过程。

采用软件均衡机制前,软件需确保 EQ 不会导致正在传输的数据包 Timeout。软件均衡的步骤如下:

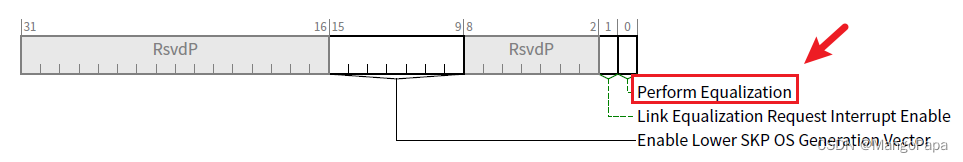

- 软件将 Link Control 3 Register (图 19)的 Perform Equalization 位置一。

- 软件填写 Link Control 2 Register (图 20)的 Target Link Speed 字段为 8 GT/s 或以上速率。

- 软件将 Link Control Register (图 21)的 Retrain Link 位置一。

若采用软件均衡机制,在使能 DSP 的 Perform Equalization 位之前,建议通过软件将 DSP 及 USP Link Control Register 的 Hardware Autonomous Width Disable 位置一,防止均衡出现问题后链路自动切换链路宽度(减宽)。对于已经启动自动减宽的设备,LTSSM 需要在 Hardware Autonomous Width Disable 位置一后的 1ms 内进 Recovery 及 Configuration 状态,重新协商链路宽度为自动切换前的链路宽度。

若 USP 未开启 8 GT/s、16 GT/s、32 GT/s 等速率,也未采用自动均衡机制,软件需确保 USP 进 Recovery 进行 EQ 对正在发的数据包没有影响。USP 进 Recovery 并建议了新的速率后,DSP 切换速率为 USP 建议的速率并开始 EQ。

对于 8 GT/s 以上速率,如果不支持或未开启 Equalization bypass to highest rate 能力,必须确保 8 GT/s 到该速率间的所有速率都成功完成了 EQ,才能针对该速率进行 EQ。

软件均衡机制不受 DLLP Blocking 机制的限制。

无论自动均衡还是软件均衡,DSP 在切速的时候,把速度切为下次要做 EQ 的速度,并表明不支持比下次 EQ 速度更高的速率。比如最高速率为 16 GT/s,预期在 8 GT/s 及 16 GT/s 时都要做一次 EQ。第一次 EQ 的时候,DSP 应建议 2.5 GT/s 切到 8 GT/s,并表明目前不支持 16 GT/s 等更高的速率。EQ 成功达到 8 GT/s 后,DSP 再切到 16 GT/s,进 Recovery 进行第二次 EQ。

3.1.2 均衡加速与关闭

Full equalization mode,全均衡模式, 是最传统的 PCIe 均衡模式。通常情况下,在指定目标速率的链路训练过程中,采用全均衡模式,先针对较低速率进行均衡,再进行较高速率的均衡,直到完成目标速率均衡。随着 PCIe 传输速率的上升,需要 EQ 的次数越来越多(单次约100 ms),EQ 耗时越来较久,影响了系统性能。为了节省均衡耗时,从 PCIe Gen5 开始,PCIe 支持跨过一些中间速率的均衡,对于原生传输质量极好的链路,也可以关闭均衡。

3.1.2.1 Equalization bypass to highest rate

对于双方都支持 32 GT/s 及以上的设备,有可能根本不会工作在 8 GT/s 或 16 GT/s,此时可以跳过 8 GT/s 和 16 GT/s 的 EQ,直接进行 32 GT/s 或以上速率的 EQ。

只有双方设备均支持且开启了 Equalization bypass to highest rate 时才能跳过中间速率的 EQ。设备是否支持该能力,取决于 32 GT/s 能力寄存器相关字段(图 22),软件可以配置 32 GT/s 控制寄存器(图 23)来关闭该能力。链路训练过程中,双方设备在 LTSSM Configuration 状态通过交换 TS 来协商是否使用 Equalization bypass to highest rate。 注意,如果是 Standard TS ,该字段位于 TS Symbol 5 的 bit[7:6];如果是 Modified TS,该字段位于 TS Symbol 5 的 bit[0]。

如果协商后决定采用 Bypass equalization to highest rate 模式进行链路训练,只进行一次切速,即链路到达 2.5 GT/s L0 后,返回 Recovery 直接切速到最高速率并针对最高速率(32 GT/s 或以上)进行 1 次 EQ。对于两端有能力最高支持 32 GT/s 及以上速率的设备,如果把目标速度设置为 8 GT/s 或 16 GT/s 速率,是不建议采用 Bypass equalization to highest rate 模式的,即便采用了,也不会针对 8 GT/s 或 16 GT/s 的目标速率进行 EQ。

开启 Equalization bypass to highest rate 后,如果在最高速率 EQ 失败且重复 EQ 也失败,就要考虑降速了。这时要注意,DSP 此时要关掉 Equalization bypass to highest rate 及 No equalization needed,从 2.5 GT/s 或 5 GT/s 老老实实往上(8 GT/s+)切速,每次都做 EQ。

3.1.2.2 No equalization needed

如果双方支持 32 GT/s 及以上速率且支持 No equalization needed,在链路质量极好或本地存有之前均衡预设好的值的前提下,我们是有信心 5 GT/s 以上速率不用 EQ 的。不做 EQ能够大大节省 EQ 的时间,以最快速度建立连接。

只有双方设备均支持且开启了 No equalization needed 时才能关闭 EQ。设备是否支持该能力,取决于 32 GT/s 能力寄存器相关字段(图 22),软件可以配置 32 GT/s 控制寄存器(图 23)来关闭该能力。链路训练过程中,双方设备在 LTSSM Configuration 状态通过交换 TS 来协商是否使用 No equalization。 注意,如果是 Standard TS,该字段位于 TS Symbol 5 的 bit[7:6];如果是 Modified TS, 该字段位于 TS Symbol 5 的 bit[1]。 Modified TS 中,如果开了 No equalization,那 Equalization bypass to highest rate 也必须置一,Equalization bypass to highest rate 置零的链路操作 spec 中未定义。

如果协商后决定采用 No equalization needed 模式进行链路训练,链路到达 2.5 GT/s L0 后,返回 Recovery 直接切速到最高速率且不做 EQ。对于两端有能力最高支持 32 GT/s 及以上速率的设备,如果把目标速度设置为 8 GT/s 或 16 GT/s 速率,是不建议采用 No equalization needed 模式的。非要采用的话,也行,同样不会针对 8 GT/s 或 16 GT/s 等任何速率进行 EQ,但是链路信号质量得不到保证。

双方设备在沟通均衡需求的时候,如果一方要求 No equalization 而令一方要求 Equalization bypass to highest rate 该怎么办呢?要求 No equalization 的一方都可以不做 EQ 了,那也不在乎再来一次 EQ。对于要求 Equalization bypass to highest rate 的设备而言,不做 EQ 的话,链路质量可能会很糟糕。保守起见按照 Equalization bypass to highest rate 进行训练。

如上文所述,Equalization bypass to highest rate 是 Gen5 的 Capability,仅 Gen5 设备 32 GT/s 可以使用。No equalization needed 不同于 Equalization bypass to highest rate,No equalization needed 是Gen5 的 Capability,如果设备支持 32 GT/s 的话,可以在任何速率建议 No equalization needed,任何中间速率都不会进行 EQ。

3.1.3 均衡结果判别及措施

均衡是否成功,是针对 8 GT/s 以上传输速率而言的,本质上是要看传输误码率性能。在某一传输速率下,通过单独调整每一条 Lane 的收发端均衡器系数,使得链路上所有有效 Lane 上的传输误码率 BER≤10-12 即认为该速率均衡完成。如果在一定时间内无法达到 BER≤10-12 的通信性能,则认为当前速率均衡失败。

3.1.3.1 均衡成功的标志

从均衡过程上讲,均衡成功意味着 LTSSM.Equalization 成功完成了 Phase 0/1 ~ Phase 3 的跳转并正常跳转到了下一状态。均衡过程中,每完成一个 Phase,PCIe Controller 中都会把当前速率的状态寄存器中相应的 Equalization Phase Successful 置一,并在完成 Phase 3 并退出均衡后将该速率的 Equalization Complete 位置一。对于 8 GT/s,寄存器名称为 Link Status 2 Reister(图 24);对于 16 GT/s,寄存器名称为 16 GT/s Status Reister(图 25);对于 32 GT/s,寄存器名称为 32 GT/s Status Reister(图 26)。

3.1.3.2 重新均衡机制

3.1.3.2.1 何时重新 EQ ?

当发生几下几种情况时,可以重新进行 EQ:

- 针对某速率均衡失败;

- 针对某速率均衡成功,但在检查均衡系数设置时发现了问题;

- 改变链路宽度。

3.1.3.2.1.1 均衡失败

针对某一速率进行 EQ 失败后,可以针对该速率重新进行 EQ,也可以降速。针对同一速率多次重复 EQ 有可能会干扰软件对链路及设备状态的判断。

如果采用重新 EQ 的方案,针对该速率重复 EQ 的次数 Spec 中未指定,但应该是有限次数。在有限次数内仍未成功 EQ,意味着当前链路的确不适合工作在当前速率,可以降一档速度试试。有两种降速方案:① Recovery.Equalization 超时进入 Recovery.Speed 掉到之前的速率;②主动发起较低速率的变速请求。一旦针对有问题的速率启动了 EQ,需确保所有检测到有问题的速率都请求一次 EQ。为了防止降速后仍然 EQ 失败,可以从较低的中间速率开始 EQ。比如:当前速率为 2.5 GT/s 或 5 GT/s,DSP 针对 32 GT/s 均衡失败,想要降速到 16 GT/s ,DSP 先切速到 8 GT/s 再切速到 16 GT/s。

链路针对某一速率 A 协商失败并成功降速到 B 后,从 B 进入 L0 开始算,200 ms 内不能针对速率 A 及以上速率进行协商,但对端主动启动 EQ 进行速率变化不受 200ms 的时间限制。

3.1.3.2.1.2 均衡设置问题

按照协议,PCIe USP 需在 Recovery.RcvrLock 状态检测 EQ 参数设置问题。此外,DSP 及 USP 随时都可以按照自定义的机制检测 EQ 参数设置问题。若检测到对端发来的 TS 中相关均衡系数跟之前协商好的参数不同,即判定 EQ 系数设置出现了问题。若 DSP 检测到 EQ 问题,或 USP 请求重新 EQ(TS2 Symbol 6 bit[7]),DSP 可以在进入 EQ 预期速率之前重新针对该速率进行 EQ,也可以针对更高的速率进行 EQ。

3.1.3.2.1.3 改变链路宽度

在满足系统带宽需求的情况下,为了降低功耗,DSP 可以降低链路宽度,USP 也可以主动请求降低链路宽度。自动均衡机制的设备在改变链路宽度之前需要重新进行 EQ。

3.1.3.2.2 重新 EQ 过程

当某 Port 检测到 EQ 设置出现问题后,该 Port 需采取以下措施重新请求 EQ:

- 对于 8 GT/s,Link Status 2 Regiser 的 Link Equanlization Requset 8 GT/s 位置一。

- 对于 16 GT/s,16 GT/s Status Register 的 Link Equanlization Requset 16 GT/s 位置一。

- 对于 32 GT/s,32 GT/s Status Register 的 Link Equanlization Requset 32 GT/s 位置一。

3.1.3.2.2.1 DSP 请求重新 EQ

只有在确保 DSP 启动 EQ 不会对 DSP 和 USP 的其他操作产生影响的前提下,DSP 才能启动 EQ 进程。如果 DSP 不确定 EQ 会对 USP 产生何影响,其可以将其链路状态寄存器中相应速率的 Link Equanlization Requset 位置一,通过发送 Quiesce Guarantee 位为一的 TS 来告知 USP 自己准备好了,并由 USP 发起 EQ。

USP 收到 DSP 的 EQ 请求后,可以(非必须)暂停其正在执行的操作,并按照收到 DSP 的 EQ 请求,再次向 DSP 发起相同速率的 EQ 请求(TS2 的 Quiesce Guarantee 位必须置一)。USP 响应 DSP EQ 请求的时间没有限制,但应尽快执行。DSP 收到 USP 响应后,在保证 EQ 对自身操作没有影响的前提下,需要在 1ms 内发起 EQ,否则把相应速率的 Link Equanlization Requset 位置一稍后再来一次。

3.1.3.2.2.2 USP 请求重新 EQ

当 USP 请求重新 EQ 时,除了将相应的 Link Equanlization Requset 位置一外,USP 进 Recovery 状态,在 Recovery.RcvrCfg 状态时给 DSP 发送 TS2, Request Equalization (TS2 Symbol 6 bit[7]) 位置一,Equalization Request Data Rate (TS2 Symbol 6 bit[5:4]) 置为需要 EQ 的速率,Quiesce Guarantee (TS2 Symbol 6 bit[6]) 位可以(非必须)置一,通知 DSP 其在 1 ms 内将启动 EQ,以确保不会对 DSP 其他操作产生影响。

DSP 收到 USP 的 EQ 请求后(处于 Recovery.RcvrCfg 且连续收到 8 个 Request Equalization 位置一的 TS2),可以(非必须)依照 USP 发来 TS2 中的 Quiesce Guarantee 位来判断是否会对 USP 产生影响。只有在确保 DSP 启动 EQ 不会对 DSP 和 USP 的其他操作产生影响的前提下,DSP 才能启动 EQ 进程。如果 DSP 确定 EQ 不会对 DSP 和 USP 的其他操作产生影响,其需要在 1ms 内按照 USP 请求的 EQ 速率发起 EQ 进程。否则,DSP 链路状态寄存器中相应速率的 Link Equanlization Requset 位置一,由 DSP 作为 EQ 请求方,查询 USP 状态(Quiesce Guarantee 位置一)。

3.1.3.2.2.3 Quiesce Guarantee 机制

Quiesce Guarantee,静默保证,是 TS 中的一个字段(Symbol 6 bit[6]),常用于 DL_Active 之后重新进行 EQ 的情况。Quiesce Guarantee 是一种可选的手段,跟 TS 中的 Request Equalization、Equalization Request Data Rate 字段配合使用。

链路工作在 8 GT/s 或以上速率时,如果 DSP 检测到 EQ 问题或者 USP 想要重新 EQ,则需要重新进行 EQ。此时 DL 层可能正在进行数据传输,如果贸然启动 EQ,有可能会在 Port、Device、System 层面引发错误。比如,DSP 发起了一笔 MRd,在 收到 CplD 之前进入 EQ,鉴于 EQ 耗时较久,会导致 Completion Timeout。Quiesce Guarantee 正是这样一种机制,告知对端我已准备好,你随时可以发起 EQ。

3.1.3.2.2.4 Perform Equalization 与 Link Equalization Request 有何区别?

Perform Equalization 位于 Link Control 3 Register,软件均衡机制中,DSP 通过使能该位来启动均衡。当 Target Link Speed 为 8 GT/s 及以上且 Retrain Link 位置一时,若 Perform Equalization 为 1,则 DSP 必须启动均衡过程。当设备为 USP 且不支持 Crosslink 时,该字段为 Reserverd。若 Port 不支持 8 GT/s,该字段为 0。

Link Equalization Request 是用来请求对具体传输速率进行均衡的,具体可分为 Link Equalization Request 8 GT/s、16 GT/s 及 32 GT/s,DSP 及 USP 都可以用。

3.1.4 不同情况下的 EQ 需求

以下规则适用于初次 EQ、重新 EQ、自动均衡、软件均衡。

3.1.4.1 切速中的 EQ

3.1.4.1.1 2.5 GT/s -> 8 GT/s 或 5 GT/s -> 8 GT/s

在沟通好要切速到 8 GT/s 之后、切换到 8 GT/s 之前,DSP 在 Recovery.RcvrCfg 状态采用 EQ TS2 给 USP 发送 Tx Preset 及 Rx Preset Hints(该字段仅用于 8 GT/s)。Tx Preset 及 Rx Preset Hints 是一组 Preset 的编码,并不指定具体的均衡器系数。DSP 此时发送的 8 GT/s EQ Preset 值为 USP Preset 值,存放在各条 Lane 的 EQ 控制寄存器中(图 27,图 28)。

在切换到要进行 EQ 的速率之后,USP 基于收到的 Preset 调整其均衡器系数反馈 TS1 到 DSP。若 Tx 采用 Reduced Swing,Preset 系数需要在其允许的动态范围之内。

在切换到要进行 EQ 的速率之后,DSP 通过 TS1 发送 Preset 值。若 Tx 采用 Reduced Swing,Preset 系数需要在其允许的动态范围之内。DSP 此时发送的 8 GT/s EQ Preset 值为 DSP Preset 值,存放在各条 Lane 的 EQ 控制寄存器中。

为了启动 8 GT/s EQ,DSP 在 2.5 GT/s 或 5 GT/s 速率的 Recovery.RcvrLock 状态通过Speed Change 位置一的 EQ TS1 请求切换速度,来通知 USP 其想要针对更高速率进行 EQ。USP 在收到 Speed Change 位置一的 EQ TS1 后,若 USP 自身也有意切到更高的速率,USP 应在 Recovery 状态响应 DSP 并提议切速到更高的速率。

3.1.4.1.2 8 GT/s -> 16 GT/s 或 16 GT/s -> 32 GT/s

当协商更高速率时,DSP 采用 128b/130b 编码发送每条 Lane 的 Tx Preset 值到 USP(没有 Rx Preset Hints,Rx Preset Hints 仅用于 8 GT/s)。在沟通好要切速到更高速率之后、切换到更高速率并进行 EQ 之前,DSP 在 Recovery.RcvrCfg 状态采用 EQ TS2 发送 Tx Preset 值。DSP 此时发送的 16 GT/s 或 32 GT/s EQ Preset 值为 USP Tx Preset 值,存放在各条 Lane 的 16 GT/s(图 29)及 32 GT/s EQ 控制寄存器(图 30)中。

除了 DSP 给 USP 发送 Preset 值,还有另一种可选的方案:在沟通好要切速到更高速率之后、却换到更高速率之前,USP 可以在 Recovery.RcvrCfg 状态采用 128b/130b 编码的 EQ TS2 给 DSP 发送初始 Tx Preset 设置。这些初始 Preset 值根据各设计自行设置。数据速率切到更高速率后,USP 将其收到的 Preset 值通过 TS1 反馈给 DSP。若 DSP 在 Recovery.RcvrCfg 状态未收到 Preset 值,在切换到较高的数据速率后,DSP 通过 TS1 给 USP 发送 Tx Preset 值。DSP 此时发送的 16 GT/s 或 32 GT/s EQ Preset 值为 DSP Tx Preset 值,存放在各条 Lane 的 16 GT/s 及 32 GT/s EQ 控制寄存器中。

为了启动重新 EQ,DSP 在 Recovery.RcvrLock 状态通过 Equalization Redo 置一的 TS1 请求切换速度,来通知 USP 其想要重新进行 EQ。USP 在收到 Speed Change 位置一、 Equalization Redo 置一 的 TS1 后,若 USP 自身也有意切到更高的速率,USP 应在 Recovery 状态提议切到更高的速率。

3.1.4.1.3 2.5 GT/s -> 32 GT/s 或 5 GT/s -> 32 GT/s

只有链路支持 Bypass Equalization to Highest Data Rate 时才能直接从 2.5 GT/s 或 5 GT/s 经 EQ 到 32 GT/s。32 GT/s Capabilities Register 的 Bypass Equalization to Highest Data Rate Supported 位为 1 且 32 GT/s Control Register 的 Bypass Equalization to Highest Data Rate Disable 位为 0 时,链路支持 Bypass Equalization to Highest Data Rate。

在沟通好要切速到 32 GT/s 之后、切换到 32 GT/s 之前,DSP 在 Recovery.RcvrCfg 状态采用 EQ TS2 给 USP 发送 Tx Preset 及 Rx Preset Hints(此处存疑,不是仅用于 8 GT/s 么?)。Tx Preset 及 Rx Preset Hints 是一组 Preset 的编码,并不指定具体的均衡器系数。DSP 此时发送的 32 GT/s EQ Preset 值为 USP Preset 值,存放在各条 Lane 的 EQ 控制寄存器中(图 30)。

在切换到要进行 EQ 的速率之后,USP 基于收到的 Preset 调整其均衡器系数反馈 TS1 到 DSP。若 Tx 采用 Reduced Swing,Preset 系数需要在其允许的动态范围之内。

在切换到要进行 EQ 的速率之后,DSP 通过 TS1 发送 Preset 值。若 Tx 采用 Reduced Swing,Preset 系数需要在其允许的动态范围之内。DSP 此时发送的 8 GT/s EQ Preset 值为 DSP Preset 值,存放在各条 Lane 的 EQ 控制寄存器中。

为了启动 32 GT/s EQ,DSP 在 2.5 GT/s 或 5 GT/s 速率的 Recovery.RcvrLock 状态通过Speed Change 位置一的 EQ TS1 请求切换速度,来通知 USP 其想要针对更高速率进行 EQ。USP 在收到 Speed Change 位置一的 EQ TS1 后,若 USP 自身也有意切到更高的速率,USP 应在 Recovery 状态响应 DSP 并提议切速到更高的速率。

3.1.4.1.4 相同速率跳转的 EQ

适用于从某一速率向相同速率跳转的重新 EQ,比如从 8 GT/s -> 8 GT/s, 16 GT/s -> 16 GT/s,32 GT/s -> 32 Gt/s。这种情况下,EQ 期间采用的初始 Preset 值等于上次对该速率进行 EQ 时采用的初始 Preset 值。

3.1.4.2 Crosslink 中的 EQ

对于 Crosslink 链路,在速率较低的、Crosslink 初始化早期充当 DSP 角色的组件在进行 EQ 时仍然充当 DSP 的角色。

3.1.4.3 Loopback 或 Compliance 中的 EQ

在 Loopback 状态,Loopback Master 需要在 2.5 GT/s 或 5 GT/s 速率时将 Tx/Rx 设置通过 EQ TS1 发送给 Slave,在 8 GT/s 或更高速率时通过 TS1 将 Preset 及 系数设置发送给 Slave。同样,若在 8 GT/s 或更高速率时通过 TS1 进入了 Polling.Compliance 状态,对设备进行 Compliance 测试的实体应通过 EQ TS1 给待测设备发送相关系数。

3.2 PCIe 均衡系数协商

PCIe 在链路训练过程中进行均衡系数的协商,进行均衡技术协商的 LTSSM 状态为 Recovery.Equalization。Recovery 子状态转移如图 31 所示。

需要注意的是,LTSSM 中的 Recovery.Equalization 的确是到 Gen3 (8 GT/s) 时才有的,但均衡不是到 Gen3 才有的。2.5 GT/s 及 5 GT/s 时,信号速率相对较低,在 Tx 端采用信号去加重即可实现较好质量的信号传输,这里的信号去加重即是均衡技术的一种。由于信号去加重时参数固定,收发端无需协商,不需要 Recovery.Equaliation 这一过程进行协商。

数据速率上升到 8 GT/s 及以上后,信号传输面临的信号完整性问题更加突出,仅采用传统的去加重无法满足高质量的信号传输,需要收发端动态协商 Tx/Rx 参数来优化信号质量。均衡系数的协商分为 Phase 0 ~ Phase 3 四个阶段,其中 DSP 无需 Phase 0。

3.2.1 DSP

DSP 进入 EQ 后,即为 Phase 1。进入 Phase 1 后,DSP 首先要做的是清理均衡相关寄存器状态及 LTSSM 中的相关变量,如表 4 所述。

| 当前速率 | 寄存器或变量操作 |

|---|---|

| 8 GT/s | - 寄存器 Link Status 2 Register 中的以下字段清零: - Equalization 8 GT/s Phase 1 Successful - Equalization 8 GT/s Phase 2 Successful - Equalization 8 GT/s Phase 3 Successful - Link Equalization Request 8 GT/s - Equalization 8 GT/s Complete - 寄存器 Link Control 3 Register 中的 Perform Equalization 字段清零 - 变量 equalization_done_8GT_data_rate 置一 - 变量 start_equalization_w_preset 清零 |

| 16 GT/s | - 寄存器 16 GT/s Status Register 中的以下字段清零: - Equalization 16 GT/s Phase 1 Successful - Equalization 16 GT/s Phase 2 Successful - Equalization 16 GT/s Phase 3 Successful - Link Equalization Request 16 GT/s - Equalization 16 GT/s Complete - 寄存器 Link Control 3 Register 中的 Perform Equalization 字段清零 - 变量 equalization_done_16GT_data_rate 置一 - 变量 start_equalization_w_preset 清零 |

| 32 GT/s | - 寄存器 32 GT/s Status Register 中的以下字段清零: - Equalization 32 GT/s Phase 1 Successful - Equalization 32 GT/s Phase 2 Successful - Equalization 32 GT/s Phase 3 Successful - Link Equalization Request 32 GT/s - Equalization 32 GT/s Complete - 寄存器 Link Control 3 Register 中的 Perform Equalization 字段清零 - 变量 equalization_done_32GT_data_rate 置一 - 变量 start_equalization_w_preset 清零 |

3.2.1.1 Phase 1

Phase 1 阶段,DSP 发送 EC=01b 的 TS1。TS1 中,各条 Lane 根据当前速率独立设置其 Transmitter Preset 字段,同时设置与 Transmitter Preset 模式相匹配的 FS、LF、Post_cursor 系数。

-

Tx Preset 选用规则

- 若 Recovery.Equalization 上一状态为 Loopback.Entry,

- 若 Configuration.LinkWidthStart 阶段发送 EQ TS1进入的 Loopback.Entry,则采用 EQ TS1 指定的 Preset。

- 若 Configuration.LinkWidthStart 阶段发送标准 TS1进入的 Loopback.Entry,则采用相关机制选用合适的 Preset。

- 否则,若最近一次 Recovery.RcvfCfg 以来 DSP 连续收到了 8 个 Tx Preset 有效的 128b/130b 编码的 EQ TS2,且当前速率为 16 GT/s 或以上,则采用收到的 EQ TS2 指定的 Preset。

- 否则,若最近一次 Recovery.RcvfCfg 以来 DSP 连续收到了 8 个 Tx Preset 有效的 EQ TS2(不一定是 128b/130b 编码) 且当前速率为 32 GT/s 或以上,如果采用了 Equalization Bypass to 32 GT/s,则采用收到的 EQ TS2 指定的 Preset。

- 否则,根据当前数据速率,选用 8/16/32 GT/s Lane Equalization Control Register Entry 中 Downstream port 8/16/32 GT/s Transmitter Preset 字段字段指定的值作为 TS 的 Tx Preset Value。

- 如果相关控制寄存器中未指定 Tx Preset 值,则需要相关机制来指定。

- 若 Recovery.Equalization 上一状态为 Loopback.Entry,

-

DSP 进入 Phase 1 后可以等待 500 ns 再评估接收信息,以等待 Rx 逻辑稳定。

-

若 DSP 所有有效 Lane 上连续收到了两个 EC=01b 的 TS1 且 DSP 有意执行 Phase 2/Phase 3,则进入 Phase 2

- Rx 应在收到第一个 OS 之后 2 ms 内完成位锁定并识别出 OS

- 若速率为 8 GT/s,Link Status 2 Register 的 Equalization 8 GT/s Phase 1 Successful 位置一

- 若速率为 16 GT/s,16 GT/s Link Status Register 的 Equalization 16 GT/s Phase 1 Successful 位置一

- 若速率为 32 GT/s 且 perform_equalization_for_loopback 为 0,32 GT/s Link Status Register 的 Equalization 32 GT/s Phase 1 Successful 位置一

- 保存 TS 中的 LF、FS 备用,Phase 3 时用

-

下一状态为 Recovery.RcvrLock 的条件:DSP 所有有效 Lane 上连续收到了两个 EC=01b 的 TS1,perform_equalization_for_loopback 为 0,且 DSP 无意执行 Phase 2/Phase 3(BER≤10-12),则进入 Recovery.RcvrLock。

- 若当前数据速率为 8 GT/s,Link Status 2 Register 中的 Equalization 8 GT/s Phase 1 Successful,Equalization 8 GT/s Phase 2 Successful,Equalization 8 GT/s Phase 3 Successful 及 Equalization 8 GT/s Complete 置一。

- 若当前数据速率为 16 GT/s,16 GT/s Link Status Register 中的 Equalization 16 GT/s Phase 1 Successful,Equalization 16 GT/s Phase 2 Successful,Equalization 16 GT/s Phase 3 Successful 及 Equalization 16 GT/s Complete 置一。

- 若当前数据速率为 32 GT/s,32 GT/s Link Status Register 中的 Equalization 32 GT/s Phase 1 Successful,Equalization 32 GT/s Phase 2 Successful,Equalization 32 GT/s Phase 3 Successful 及 Equalization 32 GT/s Complete 置一。

-

下一状态为 Loopback.Entry 的条件:perform_equalization_for_loopback 为 1,且满足下列条件之一

- 所有测试 Lane 连续收到了两个 EC=01b 的 TS1 且 DSP 无意执行 Phase 2/Phase 3

- 24 ms Timeout

-

下一状态为 Recovery.Speed 的条件:perform_equalization_for_loopback 为 0 且 24 ms Timeout。然后

- success_speed_negotiation 清零

- 若当前数据速率为 8 GT/s,Link Status 2 Register 中的 Equalization 8 GT/s Complete 置一

- 若当前数据速率为 16 GT/s,16 GT/s Link Status Register 中的 Equalization 16 GT/s Complete 置一

- 若当前数据速率为 32 GT/s,32 GT/s Link Status Register 中的 Equalization 32 GT/s Complete 置一

3.2.1.2 Phase 2

-

DSP 在 Phase 2 各条 Lane 独立发送 EC=10b 的 TS1 及相关 EQ 系数。

- 若进入 Phase 2 以来连续收到 2 个 EC=10b 的 TS1

- 若最近收到的两个 TS1 中的 Preset 及系数合法且支持,

- 收到第 2 个 TS1 后的 500 ns 内,将 Tx Pin 相关参数设置为 Rx 请求的 Preset 及系数。Tx 更新设置引起的非法电平及参数持续时间不能超过 1 ns。

- 如果接受了 Rx 请求,且按照 Rx 的请求设置了发送 TS1 中的 Tx Preset、Pre-cursor、Cursor、Post-cursor 系数,那么应该把TS1 中的 Reject Coefficint Values 字段清零。

- 若 Rx 请求的 Preset 及系数不合法或 Tx 不支持,那 Tx 不能采用其请求,且应该把TS1 中的 Reject Coefficint Values 字段置一,告知 Rx 其请求被驳回。

- 若最近收到的两个 TS1 中的 Preset 及系数合法且支持,

- 否则 Tx 继续采用其当前的 Preset 及系数。

- 若进入 Phase 2 以来连续收到 2 个 EC=10b 的 TS1

-

如 DSP 在所有已配置 Lane 上连续收到了 2 个 EC=11b 的 TS1,进入 Phase 3

- 若速率为 8 GT/s,Link Status 2 Register 的 Equalization 8 GT/s Phase 2 Successful 位置一

- 若速率为 16 GT/s,16 GT/s Link Status Register 的 Equalization 16 GT/s Phase 2 Successful 位置一

- 若速率为 32 GT/s 且 perform_equalization_for_loopback 为 0,32 GT/s Link Status Register 的 Equalization 32 GT/s Phase 2 Successful 位置一

-

若 perform_equalization_for_loopback 为 1 且 32+4 ms Timeout,进入 Loopback.Entry

-

若 perform_equalization_for_loopback 为 0 且 32+4 ms Timeout,进入 Recovery.Speed

- success_speed_negotiation 清零

- 若当前数据速率为 8 GT/s,Link Status 2 Register 中的 Equalization 8 GT/s Complete 清零

- 若当前数据速率为 16 GT/s,16 GT/s Link Status Register 中的 Equalization 16 GT/s Complete 清零

- 若当前数据速率为 32 GT/s,32 GT/s Link Status Register 中的 Equalization 32 GT/s Complete 清零

3.2.1.3 Phase 3

- DSP 在 Phase 3 发送 EC=11b 的 TS1。

- DSP 在 Phase 3 时,每条 Lane 独立评估 EQ 参数并达到最优参数设置。若 perform_equalization_for_loopback 为 1,只在测试 Lane 上进行评估并对 Preset 及 EQ 系数进行评估优化:

- 若 DSP 希望采用 Preset 值,则将其发送 TS1 中的 Tx Preset 值置为其期望的值,并把 Use Preset 位置一;若 DSP 不采用 Preset 值,则将其发送 TS1 中的 Pre-cursor、Cursor、Post-cursor 值置为其期望的值,并把 Use Preset 位置清零。一旦开始发送请求,在完成评估前至少应持续 1 us。

- DSP 的等待一段时间(500 ns + 往返时延)。在等待期间,DSP 等待 USP 完成 Tx 参数调整,DSP 可以忽略 USP 发来的数据。等待期间,若 USP 接受 DSP 的请求,USP 按照DSP 的请求其 USP 自身的 Tx 参数。等待期满,DSP 验证块对齐情况,无论是否完成块对齐,都对收到的 OS 进行评估。

- 若 DSP 连续收到 2 个 TS1,TS1 中的 Tx Preset 或 Pre-cursor、Cursor、Post-cursor 与 DSP 请求的一致,且 Reject Coefficient Value 为 0,表明 USP 接受了 DSP 的参数设置请求。这些结果可以作为候选的最终结果。

- 若 DSP 连续收到 2 个 TS1,TS1 中的 Tx Preset 或 Pre-cursor、Cursor、Post-cursor 与 DSP 请求的一致,且 Reject Coefficient Value 为 1,表明 USP 拒绝了 DSP 的参数设置请求。这些结果不可以作为候选的最终结果。

- 若一定时间内 DSP 没有收到 USP 反馈的带有与请求参数相同的 TS1,则不能采用请求的参数。

- DSP 需要根据其评估标准及需求来复位 USP 的 EIEOS Interval Counter,通过将发送 TS1 中的 Reset EIEOS Interval Counter 位置一来复位。不可以依据接收到的 TS1 中的 Use Preset 位来判断 DSP 的请求是否被接受。

- 什么时候来复位 EIEOS Counter 呢?DSP 想要一个较长的 PRBS Pattern 时可以将 Reset EIEOS Interval Count 置一,在需要 Block Alignment 的时候将其清零。

- Preset 及系数请求:Phase 3 时 DSP 发送的所有 TS1 均为请求。第一次发送的请求中,可以为新的 Preset 或系数集(请求调整),也可以为连续接收到的 2 个 EC=11b 的 TS1 中的 Preset 及系数(请求对端保留当前设置)。

- 每次 Preset 或系数请求应在 2 ms 内完成。在优化的最后阶段,需要更长评估时间(时间少了无法完成评估),此时可以超过 2 ms 限制,但总体评估时间不能超过 24 ms,且最多只能 2 ms 超时两次。 如果请求者在超时期限内无法接收 Ordered Sets,则可能认为请求的设置在该 Lane 中不起作用。

- 所有新的 Preset 或系数设置必须同时出现在所有配置的通道上。 如果当时不想更改设置,则允许任何给定通道继续传输当前预设或系数作为其新值。

- 若当前速率为 32 GT/s 且 perform_equalization_for_loopback 为 1,满足以下条件时,下一状态为 Loopback.Entry。

- 测试中的 Lane 工作在了最优设置,且所有 Lane 上连续收到了 2 个 Retimer Equalization Extent 位为 0 的 TS1。

- 24+2 ms Timeout。

- 若 perform_equalization_for_loopback 为 0,所有配置 Lane 工作在最优设置下,且满足以下两个条件之一(①当前速率为 8 GT/s;②所有 Lane 上连续收到了 2 个 Retimer Equalization Extent 位为 0 的 TS1),下一状态为 Recovery.RcvrLock。

- 若速率为 8 GT/s,Link Status 2 Register 的 Equalization 8 GT/s Phase 3 Successful 及 Equalization 8 GT/s Complete 位置一。

- 若速率为 16 GT/s,16 GT/s Link Status Register 的 Equalization 16 GT/s Phase 3 Successful 及 Equalization 16 GT/s Complete 位置一。

- 若速率为 32 GT/s,32 GT/s Link Status Register 的 Equalization 32 GT/s Phase 3 Successful 及 Equalization 32 GT/s Complete 位置一。

- 否则,24+2 ms Timeout 后,下一状态为 Recovery.Speed。

- success_speed_negotiation 清零。

- 若当前数据速率为 8 GT/s,Link Status 2 Register 中的 Equalization 8 GT/s Complete 位置一。

- 若当前数据速率为 16 GT/s,16 GT/s Link Status Register 中的 Equalization 16 GT/s Complete 位置一。

- 若当前数据速率为 32 GT/s,32 GT/s Link Status Register 中的 Equalization 32 GT/s Complete 位置一。

3.2.2 USP

USP 进入 EQ 后,为 Phase 0。进入 Phase 0 后,USP 首先要做的是清理均衡相关寄存器状态及 LTSSM 中的相关变量,如表 5 所述。

| 当前速率 | 寄存器或变量操作 |

|---|---|

| 8 GT/s | - 寄存器 Link Status 2 Register 中的以下字段清零: - Equalization 8 GT/s Phase 1 Successful - Equalization 8 GT/s Phase 2 Successful - Equalization 8 GT/s Phase 3 Successful - Link Equalization Request 8 GT/s - Equalization 8 GT/s Complete - 变量 equalization_done_8GT_data_rate 置一 - 变量 start_equalization_w_preset 清零 |

| 16 GT/s | - 寄存器 16 GT/s Status Register 中的以下字段清零: - Equalization 16 GT/s Phase 1 Successful - Equalization 16 GT/s Phase 2 Successful - Equalization 16 GT/s Phase 3 Successful - Link Equalization Request 16 GT/s - Equalization 16 GT/s Complete - 变量 equalization_done_16GT_data_rate 置一 - 变量 start_equalization_w_preset 清零 |

| 32 GT/s | - 寄存器 32 GT/s Status Register 中的以下字段清零: - Equalization 32 GT/s Phase 1 Successful - Equalization 32 GT/s Phase 2 Successful - Equalization 32 GT/s Phase 3 Successful - Link Equalization Request 32 GT/s - Equalization 32 GT/s Complete - 变量 equalization_done_32GT_data_rate 置一 - 变量 start_equalization_w_preset 清零 |

注:没有寄存器 Link Control 3 Register 中的 Perform Equalization 相关操作,这是 DSP 的。

3.2.2.1 Phase 0

Phase 0 阶段,USP 发送 EC=00b 的 TS1。TS1 中,各条 Lane 根据当前速率独立设置其 Transmitter Preset 字段,同时设置与 Transmitter Preset 模式相匹配的 FS、LF、Post_cursor 系数。

- Recovery.Equalization 上一状态为 Loopback.Entry 时,

- 若 Configuration.LinkWidthStart 阶段发送 EQ TS1进入的 Loopback.Entry,则采用 EQ TS1 指定的 Preset。

- 若 Configuration.LinkWidthStart 阶段发送标准 TS1进入的 Loopback.Entry,则采用相关机制选用合适的 Preset。

- 若当前速率为 8 GT/s,USP 采用其在最近一次 2.5 GT/s 或 5 GT/s 时收到的 EQ TS2 中的 Tx Preset 设置 USP 的 Tx 均衡器,并反馈 TS1 给 DSP。

- 若当前速率为 16 GT/s,USP 采用其在最近一次 8 GT/s 时收到的 EQ TS2 中的 Tx Preset 设置 USP 的 Tx 均衡器,并反馈 TS1 给 DSP。

- 若当前速率为 32 GT/s 且 perform_euqualization_for_loopback 为 0,USP 采用其在最近一次 2.5 GT/s、5 GT/s 或 16 GT/s 时收到的 EQ TS2 中的 Tx Preset 设置 USP 的 Tx 均衡器,并反馈 TS1 给 DSP。

- 若 USP 某条 Lane 收到了 Reserved 或不支持的 Tx Preset,该 Lane 可以根据具体情况采用任一支持的 Tx Preset 设置,但反馈给 DSP 的 TS1 中仍然采用其收到的无效的 Preset,并把 Reject Coefficient 置一通知 DSP 发送的 Preset 被拒绝。

- 若 USP 某条 Lane 此前未收到 EQ TS2,该 Lane 可以根据具体情况采用任一支持的 Tx Preset 设置,把其采用的 Preset 及均衡器系数通过 TS1 反馈给 DSP,并把 Reject Coefficient 不置一。

- USP 进入 Phase 0 后可以等待 500 ns 再评估接收信息,以等待 Rx 逻辑稳定。

- 若 USP 所有有效 Lane 上连续收到了两个 EC=01b 的 TS1,USP 进入 Phase 1。

- Rx 应在收到第一个 OS 之后 2 ms 内完成位锁定并识别出 OS。

- 保存 TS 中的 LF、FS 备用,Phase 2 时用

- 若 perform_equalization_for_loopback 为 1 且 12 ms Timeout,则跳转到 Loopback.Entry

- 若 perform_equalization_for_loopback 为 0 且 12 ms Timeout,则跳转到 Recovery.Speed,然后

- success_speed_negotiation 清零

- 若当前数据速率为 8 GT/s,Link Status 2 Register 中的 Equalization 8 GT/s Complete 置一

- 若当前数据速率为 16 GT/s,16 GT/s Link Status Register 中的 Equalization 16 GT/s Complete 置一

- 若当前数据速率为 32 GT/s,32 GT/s Link Status Register 中的 Equalization 32 GT/s Complete 置一

3.2.2.2 Phase 1

-

Phase 1 阶段,USP 基于 Phase 0 的 Preset 设置其 Tx 均衡器并发送 EC=01b 的 TS1。TS1 中,各条 Lane 根据当前速率独立设置其 Transmitter Preset 字段,同时设置与 Transmitter Preset 模式相匹配的 FS、LF、Post_cursor 系数。

-

若 USP 所有有效 Lane 上连续收到了两个 EC=10b 的 TS1,则进入 Phase 2

- 若速率为 8 GT/s,Link Status 2 Register 的 Equalization 8 GT/s Phase 1 Successful 位置一

- 若速率为 16 GT/s,16 GT/s Link Status Register 的 Equalization 16 GT/s Phase 1 Successful 位置一

- 若速率为 32 GT/s 且 perform_equalization_for_loopback 为 0,32 GT/s Link Status Register 的 Equalization 32 GT/s Phase 1 Successful 位置一

-

下一状态为 Recovery.RcvrLock 的条件:USP 所有有效 Lane 上连续收到了 8 个 EC=00b 的 TS1,perform_equalization_for_loopback 为 0,则进入 Recovery.RcvrLock。

- 若当前数据速率为 8 GT/s,Link Status 2 Register 中的 Equalization 8 GT/s Phase 1 Successful 及 Equalization 8 GT/s Complete 置一。

- 若当前数据速率为 16 GT/s,16 GT/s Link Status Register 中的 Equalization 16 GT/s Phase 1 Successful 及 Equalization 16 GT/s Complete 置一。

- 若当前数据速率为 32 GT/s,32 GT/s Link Status Register 中的 Equalization 32 GT/s Phase 1 Successful 及 Equalization 32 GT/s Complete 置一。

-

下一状态为 Loopback.Entry 的条件:perform_equalization_for_loopback 为 1,且满足下列条件之一

- USP 所有测试 Lane 连续收到了两个 EC=00b 的 TS1

- 12 ms Timeout

-

下一状态为 Recovery.Speed 的条件:perform_equalization_for_loopback 为 0 且 12 ms Timeout。然后

- success_speed_negotiation 清零

- 若当前数据速率为 8 GT/s,Link Status 2 Register 中的 Equalization 8 GT/s Complete 置一

- 若当前数据速率为 16 GT/s,16 GT/s Link Status Register 中的 Equalization 16 GT/s Complete 置一

- 若当前数据速率为 32 GT/s,32 GT/s Link Status Register 中的 Equalization 32 GT/s Complete 置一

3.2.2.3 Phase 2

- USP 在 Phase 3 发送 EC=10b 的 TS1。

- USP 在 Phase 3 时,每条 Lane 独立评估 EQ 参数并达到最优参数设置。若 perform_equalization_for_loopback 为 1,只在测试 Lane 上进行评估并对 Preset 及 EQ 系数进行评估优化:

- 若 USP 希望采用 Preset 值,则将其发送 TS1 中的 Tx Preset 值置为其期望的值,并把 Use Preset 位置一;若 DSP 不采用 Preset 值,则将其发送 TS1 中的 Pre-cursor、Cursor、Post-cursor 值置为其期望的值,并把 Use Preset 位置清零。一旦开始发送请求,在完成评估前至少应持续 1 us。

- USP 的等待一段时间(500 ns + 往返时延)。在等待期间,USP 等待 DSP 完成 Tx 参数调整,USP 可以忽略 DSP 发来的数据。等待期间,若 DSP 接受 USP 的请求,DSP 按照 USP 的请求其 DSP 自身的 Tx 参数。等待期满,USP 验证块对齐情况,无论是否完成块对齐,都对收到的 OS 进行评估。

- 若 DSP 连续收到 2 个 TS1,TS1 中的 Tx Preset 或 Pre-cursor、Cursor、Post-cursor 与 DSP 请求的一致,且 Reject Coefficient Value 为 0,表明 DSP 接受了 USP 的参数设置请求。这些结果可以作为候选的最终结果。

- 若 DSP 连续收到 2 个 TS1,TS1 中的 Tx Preset 或 Pre-cursor、Cursor、Post-cursor 与 DSP 请求的一致,且 Reject Coefficient Value 为 1,表明 DSP 拒绝了 USP 的参数设置请求。这些结果不可以作为候选的最终结果。

- 若一定时间内 USP 没有收到 DSP 反馈的带有与请求参数相同的 TS1,则不能采用请求的参数。

- USP 需要根据其评估标准及需求来复位 DSP 的 EIEOS Interval Counter,通过将发送 TS1 中的 Reset EIEOS Interval Counter 位置一来复位。不可以依据接收到的 TS1 中的 Use Preset 位来判断 USP 的请求是否被接受。

- 什么时候来复位 EIEOS Counter 呢?USP 想要一个较长的 PRBS Pattern 时可以将 Reset EIEOS Interval Count 置一,在需要 Block Alignment 的时候将其清零。

- Preset 及系数请求:Phase 2 时 USP 发送的所有 TS1 均为请求。第一次发送的请求中,可以为新的 Preset 或系数集(请求调整),也可以为连续接收到的 2 个 EC=10b 的 TS1 中的 Preset 及系数(请求对端保留当前设置)。

- 每次 Preset 或系数请求应在 2 ms 内完成。在优化的最后阶段,需要更长评估时间(时间少了无法完成评估),此时可以超过 2 ms 限制,但总体评估时间不能超过 24 ms,且最多只能 2 ms 超时两次。 如果请求者在超时期限内无法接收 Ordered Sets,则可能认为请求的设置在该 Lane 中不起作用。

- 所有新的 Preset 或系数设置必须同时出现在所有配置的通道上。 如果当时不想更改设置,则允许任何给定通道继续传输当前预设或系数作为其新值。

- 若 perform_equalization_for_loopback 为 1,测试中的 Lane 工作在了最优设置,且所有 Lane 上连续收到了 2 个 Retimer Equalization Extent 位为 0 的 TS1,下一状态为 Phase 3。

- 若 perform_equalization_for_loopback 为 0,所有配置 Lane 工作在最优设置下,且满足以下两个条件之一(①当前速率为 8 GT/s;②所有 Lane 上连续收到了 2 个 Retimer Equalization Extent 位为 0 的 TS1),下一状态为 Recovery.RcvrLock。

- 若速率为 8 GT/s,Link Status 2 Register 的 Equalization 8 GT/s Phase 2 Successful 位置一。

- 若速率为 16 GT/s,16 GT/s Link Status Register 的 Equalization 16 GT/s Phase 2 Successful 位置一。

- 若速率为 32 GT/s,32 GT/s Link Status Register 的 Equalization 32 GT/s Phase 2 Successful 位置一。

- 若 perform_equalization_for_loopback 为 1 且 24+2 ms Timeout,下一状态为 Loopback.Entry。

- 否则,24+2 ms Timeout 后,下一状态为 Recovery.Speed。

- success_speed_negotiation 清零。

- 若当前数据速率为 8 GT/s,Link Status 2 Register 中的 Equalization 8 GT/s Complete 位置一。

- 若当前数据速率为 16 GT/s,16 GT/s Link Status Register 中的 Equalization 16 GT/s Complete 位置一。

- 若当前数据速率为 32 GT/s,32 GT/s Link Status Register 中的 Equalization 32 GT/s Complete 位置一。

3.2.2.4 Phase 3

-

USP 在 Phase 3 各条 Lane 独立发送 EC=11b 的 TS1 及相关 EQ 系数。

- 若进入 Phase 3 以来连续收到 2 个 EC=11b 的 TS1

- 若最近收到的两个 TS1 中的 Preset 及系数合法且支持,

- 收到第 2 个 TS1 后的 500 ns 内,将 Tx Pin 相关参数设置为 Rx 请求的 Preset 及系数。Tx 更新设置引起的非法电平及参数持续时间不能超过 1 ns。

- 如果接受了 Rx 请求,且按照 Rx 的请求设置了发送 TS1 中的 Tx Preset、Pre-cursor、Cursor、Post-cursor 系数,那么应该把TS1 中的 Reject Coefficint Values 字段清零。

- 若 Rx 请求的 Preset 及系数不合法或 Tx 不支持,那 Tx 不能采用其请求,且应该把TS1 中的 Reject Coefficint Values 字段置一,告知 Rx 其请求被驳回。

- 若最近收到的两个 TS1 中的 Preset 及系数合法且支持,

- 否则 Tx 继续采用其当前的 Preset 及系数。

- 若进入 Phase 3 以来连续收到 2 个 EC=11b 的 TS1

-

如 USP 在所有已配置 Lane 上连续收到了 2 个 EC=00b 的 TS1,进入 Recovery.RcvrLock

- 若速率为 8 GT/s,Link Status 2 Register 的 Equalization 8 GT/s Phase 3 Successful 及 Equalization 8 GT/s Complete 位置一。

- 若速率为 16 GT/s,16 GT/s Link Status Register 的 Equalization 16 GT/s Phase 3 Successful 及 Equalization 16 GT/s Complete 位置一。

- 若速率为 32 GT/s,32 GT/s Link Status Register 的 Equalization 32 GT/s Phase 3 Successful 及 Equalization 32 GT/s Complete 位置一。

-

若 perform_equalization_for_loopback 为 1 且 USP 在所有测试 Lane 上连续收到了 2 个 EC=00b 的 TS1 或 32+4 ms Timeout,进入 Loopback.Entry。

-

否则,32+2 ms Timeout 后,下一状态为 Recovery.Speed。

- success_speed_negotiation 清零。

- 若当前数据速率为 8 GT/s,Link Status 2 Register 中的 Equalization 8 GT/s Complete 位置一。

- 若当前数据速率为 16 GT/s,16 GT/s Link Status Register 中的 Equalization 16 GT/s Complete 位