一文讲清处理器GPIO内部结构和各种模式

时间:2021-12-02 11:28:00

概述

能将处理器的GPIO(General Purpose Input and Output)外部布局和种种模式彻底弄清楚的人并不多,最近在百度上搜刮了少量对于这部份的材料,关于此中不少题目的说法其实不对立。本文尽量的将IO涉及到的所有题目排列进去,关于有明确谜底的题目说明清晰,关于还存在疑难的处所也将题目提出,供人人接头。

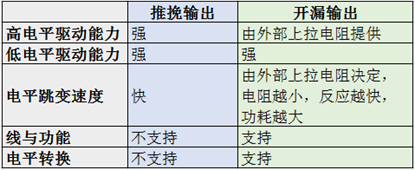

概括地说,IO的性能模式大致能够分为输出、输入以及输出输入双向三大类。此中作为基础输出IO,相对于比拟简略,首要触及的知识点便是高阻态;作为输入IO,相比于输出庞杂一些,事情模式主要有开漏(Open Drain)模式和推挽(Push-Pull)模式,这一部份触及的知识点比较多;关于输出输入IO,轻易发生迷惑的处所是准双向和双向端口的差别。

上面就根据如许的次第顺次先容各个模式的细致情形。

输出IO

这里所说的输出IO,指的是只作为输出,不具有输入性能。此时关于input引脚的请求便是高阻(高阻与三态是同一个观点)。基础输出电路的范例大致能够分为3类:基础输出IO电路、施密特触发输出电路以及弱上拉输出电路。

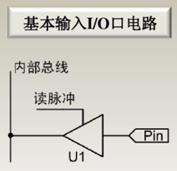

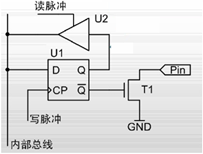

先从最基本的基础输出IO电路提及,其电路如图 1所示。

图 1

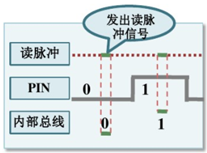

此中的缓冲器U1是拥有操纵输出端,且拥有高阻抗特点的三态缓冲器。普通地说便是这个缓冲器对外来说是高阻的,相当于在操纵输出端不使能的情况下,物理引脚与外部总线之间是完整断绝的,完整不会影响外部电路。而操纵输出端的感化便是能够收回读Pin状况的操纵指令。其进程如图 2所示。

图 2

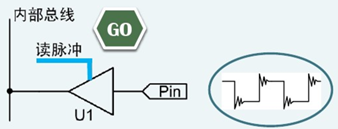

这类基础电路的一个瑕玷是在读取内部旌旗灯号的跳变沿时会涌现颤动,如下图所示。

图 3

因而施密特触发输出电路便是解决了上述这类颤动的题目,其经由施密特触发器后的旌旗灯号如图 4所示。

图 4

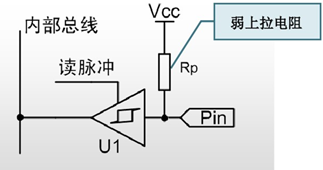

关于输出电路还存在此外一个题目,便是当输出引脚悬空的时间,输出端检测到的电平是高仍是低?当输出旌旗灯号没有被驱动,即悬空(Floating)时,输出引脚上任何的噪声都市转变输出端检测到的电平,如图 5所示。

图 5

为了解决这个题目能够输出引脚处加一个弱上拉电阻,如图 6所示。

图 6

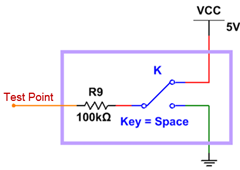

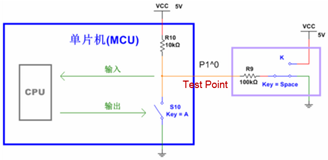

另一个问题是该电路对外显现的不是高阻,某种意思上说也在向外输入内部驱动电路不同时大概涌现谬误的检测效果比方内部驱动电路是如图 7所示布局,该电路布局经由过程K打到分歧能够输入高电平或许低电平。

图 7

图 8

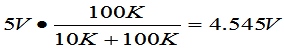

由欧姆定律知,测试点处的电平是

图 9

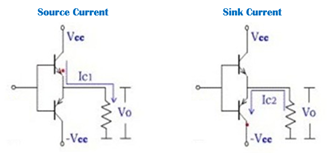

IO输入电路最主要的两种模式分别是推挽输入(Push-Pull Output输入(Open Drain Output)。

推挽输入(Push-Pull Output)

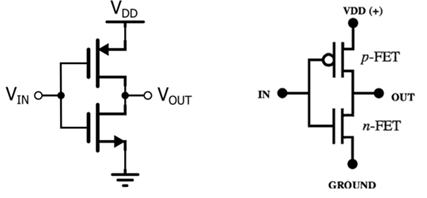

推挽输入布局是由两个三极管或许MOS遭到互补旌旗灯号操纵,两个管子一直坚持一个处于截止,另一个处于状况。如图 10所示。

图 10

推挽输入的最大特点是能够真正能真正输入高电平和低电平,在两种电平拥有驱动才能。

当然假如只是数字旌旗灯号通报,下一输出阻抗理论上最佳便是只需要传电压基础没有电流,也就没有功率,于是就不需要很大的驱动才能。

图 11

但推挽输入的一个瑕玷假如当两个推挽输入布局相连在一起,一个输入高电平下面的MOS上面的MOS适时;同时另一个输入低电平下面的MOS闭合上面的MOS导通时。电流会从第一个引脚的VCC经由过程上端MOS经由第二个引脚的下端MOS间接流向GND全部通路上电阻很小产生短路,进而大概造成端口侵害。这也是为何推挽输入不克不及完成缘故原由。

常说的与推挽输入相对于便是输入关于输入和推挽输入差别广泛的说法便是输入无奈真正输入高电平,即高电平时没有驱动才能需求借助内部上拉电阻实现对外驱动上面就从外部布局道理上说明为甚么输入输入高电平时没有驱动才能,以及进一步比拟与推挽输入差别。

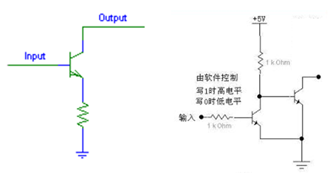

图 12

图 12右边的电路是开集(OC输入最基本的电路输出为高电平时,NPN三极管导通,Output被拉到GND输入为低电平输出为低电平时,NPN三极管闭合,Output相当于开路输入高阻)。高电平输入高阻(高阻、三态以及floating说的都是一个意义),此时对外没有任何的驱动才能便是输入最大特色若何应用特色实现种种性能稍后先容。这个电路尽管成为了输入性能然则涌现input输入为低;input输入情形。

图 12右侧的电路中多使用了一个三极管成为了"反相输出为高电平时,第一个三极管导通,此时第二个三极管输出端会被拉到GND因而第二个三极管闭合输入输出为低电平时,第一个三极管闭合,此时第二个三极管输出端会被上拉电阻拉到高电平因而第二个三极管输入被拉到GND如许,这个电路输出输入是同相的了。

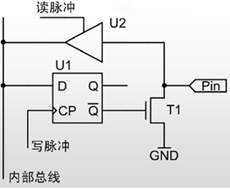

接下来先容输入的电路,如图 13所示道理输入基础沟通,只是将三极管成为了MOS罢了。

图 13

接着说说开输入特色以及使用因为二者类似,后文中若无非凡解释,则用暗示输入电路。

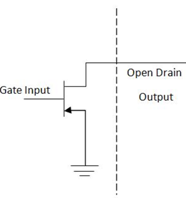

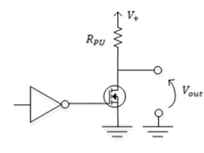

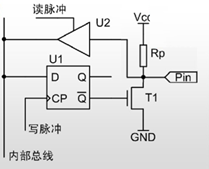

1.输入最主要特点便是高电平没有驱动才能需求借助内部上拉电阻能力真正输入高电平,其电路如图 14所示。

图 14

当MOS适时输入电路输入高电平,且连接着负载时,电流流向内部电源,流经下去电阻RPU,流进负载最初进入GND。

推挽输入差别

图 15

双向IO

图 16

双向开漏IO

图 17

准双向开漏IO

图 18

这个布局与图 17相比如下沟通分歧的地方:

1) 作为输出引脚历时必需先向U1中写"1",以达到断开T1目标以是是不是需求提早并非双向IO与准双向IO差别二者输出端口需求提早写"1"。

2) 双向端口作为输入时是真正的高阻态,而准双向IO作为输出端口输出阻抗不为因而大概涌现如本文图 8所示题目。

3) 准双向端口读取输出状况觉得便是判别内部输出旌旗灯号要领是"非低则为布局只能正确辨认内部的低电平无奈区别悬空和真正因而只需读到的不是觉得内部为1。

推挽输入作为双向IO

51单片机的P0端口

在双向端口接头比拟庞杂便是51单片机的P0端口了。这里细致接头一下51单片机的P0端口布局事情道理。

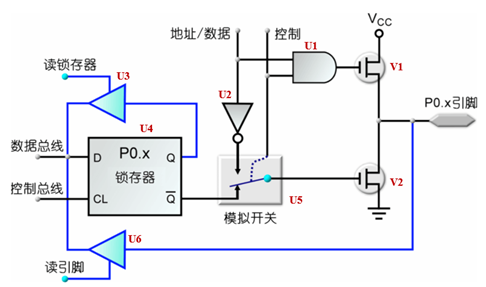

P0端口外部布局如图 19所示。

图 19

1) U1:与门。一个输出连着控制线,另一个输出连贯地点/数据旌旗灯号因为与门特点,当控制线为1时,与门输入地点/数据旌旗灯号的电平坚持同等假如控制线输入因而操纵信号线相当于与门旌旗灯号。

2) U2:反相器输入信号为地点/数据旌旗灯号的反相旌旗灯号。

3) U3和U6都是拥有操纵输出拥有高阻抗特点的三态缓冲器,作用是关于内部显现操纵能够内部旌旗灯号的电平读进数据总线。

5) U5模仿开关能够操纵V2输出旌旗灯号是来自锁存器U4输入仍是来自于反相器U2输入。

6) V1和V2分别是两个MOS管。

了解了各个自力器件以后开端先容事情在各个模式事情道理:

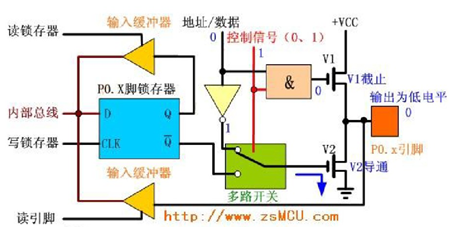

P0用于地点/数据线时:

在P0作为地点/数据线地点、数据复用总线,P0需求输入地点,同时需求读回数据旌旗灯号。

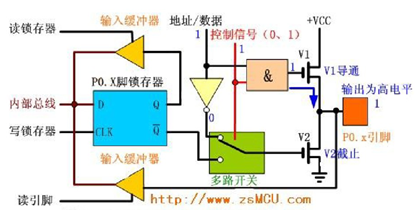

当P0需求输入地点信息时,U1操纵信号为模仿开关U5接到U2反相器输入因而地点信号线传来的信号为1,与控制线"1"相与以后输出到V1输出信号为"1",V1截止地点旌旗灯号"1"经反相以后经由过程模仿开关输出到V2输出端为"0",V2因而情形如图 20所示,pin输入"0"。

图 20

图 21

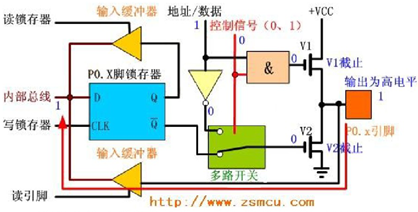

当P0输入低8位地点信息变成数据总线,此时CPU操纵操纵输入模仿开关打到锁存器的Q非端,且向锁存器中打入因而输入为0,V2截止。同时控制线为0使得与门输入为0,V1截止因为V1和V2都截止以是此时pin对外完整显现高阻,作为输出端口内部数据经由过程U6进入外部总线情形如图 22所示。(相当于将推挽输入的两个MOS全数断开了)此时因为对外显现高阻,所以是真正输出引脚。这就说明为何说P0是真正的双线端口。

图 22

P0用于一般IO时:

在P0作为一般IO并作为输入操纵信号为0,使V1一直处于截止状况模仿开关连接到输入,当作为输入输出间接输出或许1,Q非将反相旌旗灯号输出到V2输出输入"0"时,V2输出端为"1",V2导通,pin输入输入"1"时,V2输出端为"0",V2截止,pin输入高阻的0。即当P0事情一般IO模式输入输入外部没有上拉电阻。

在P0作为一般IO并作为输入时操纵信号为0,使V1一直处于截止状况模仿开关连接到输入,且CPU意向输出端写1,则V2输出端为0,V2截止以前在作为地点/数据线,作为输入时同样,也是两个MOS全数断开,pin间接连接到U6,对外显现因而也是真正输出引脚。

综上P0无论事情哪类模式下都是真正的双端口IO。

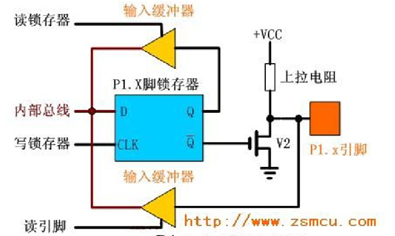

51单片机的P1~P3端口

51单片机其余三个端口外部布局如图 23所示,与P0相比简略不少,没有了顶部的MOS管,也没有地点/数据旌旗灯号的选项。作为输入时是带有上拉电阻输入,作为输入时是有上拉电阻存在因而输出端口对外不是高阻。这就说明为何P1~P3只能是准双向端口。

图 23