TSB83AA23ZAY

IEEE标准1394B -2002 PHY和OHCI Link设备 IEEE Std 1394b-2002 PHY AND OHCI LINK DEVICE

Description

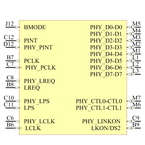

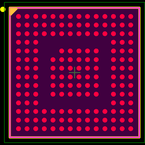

The TSB83AA23 is an integrated IEEE Std 1394b-2002 link-layer controller LLC design and physical layer PHY design combined in a single package to meet the demanding requirements of today’s 1394 bus applications. The TSB83AA23 device is capable of exceptional 800-Mbps performance; thus, providing the throughput and bandwidth to move data efficiently and quickly between the PCI and 1394 buses. The TSB83AA23 device also provides outstanding ultralow power operation and intelligent power-management capabilities. The device provides the IEEE 1394 LLC function and PHY function and is compatible with 100-Mbps, 200-Mbps, 400-Mbps, and 800-Mbps serial-bus data rates.

Features

• Fully Supports Provisions of IEEE Std 1394b-2002 Revision 1.33+ at 1-Gigabit Signaling Rates

• Fully Supports Provisions of IEEE Std 1394a-2000 and IEEE Std 1394-1995 for High-Performance Serial Bus

• Fully Interoperable With Firewire™, i.LINK™, and SB1394 Implementations of IEEE Std 1394

• Provides Three Fully Backward-Compatible, IEEE Std 1394a-2000 Fully Compliant Bilingual IEEE Std 1394b-2002 Cable Ports at up to 800 Megabits per Second Mbps

• Full IEEE Std 1394a-2000 Support Includes:

– Connection Debounce

– Arbitrated Short Reset

– Multispeed Concatenation

– Arbitration Acceleration

– Fly-By Concatenation

– Port Disable/Suspend/Resume

• Extended Resume Signaling for Compatibility With Legacy Digital Video DV Devices

• Power-Down Features to Conserve Energy in Battery-Powered Applications

• Low-Power Sleep Mode

• Fully Compliant With Open Host Controller Interface OHCI Requirements

• Cable Power Presence Monitoring

• Cable Ports Monitor Line Conditions for Active Connection to Remote Node

• Register Bits Give Software Control of

Contender Bit, Power-Class Bits, Link Active

Control Bit, and IEEE Std 1394a-2000 Features

• Interoperable With Other 1394 Physical Layers PHYs Using 1.8-V, 3.3-V, and 5-V Supplies

• Low-Jitter, External Crystal Oscillator Provides Transmit and Receive Data at 100/200/400/800 Mbps and Link-Layer Controller LLC Clock at 49.152 MHz and 98.304 MHz

• Separate Bias TPBIAS for Each Port

• Software Device Reset SWR

• Fail-Safe Circuitry Senses Sudden Loss of Power to the Device and Disables Ports to Ensure That TSB83AA23 Does Not Load TPBIAS of Any Connected Device and Blocks Any Leakage From the Port Back to Power Plane

• IEEE Std 1394a-2000-Compliant Common-Mode Noise Filter on Incoming Bias Detect Circuit to Filter Out Crosstalk Noise

• Port Programmable to Force IEEE Std 1394a-2000 Mode to Allow Use of IEEE Std 1394a-2000 Connectors IEEE Std 1394b-2002 Signaling Must Not Be Put Across IEEE Std 1394a-2000 Connectors or Cables

• 3.3-V and 5-V PCI Signaling Environments

• Serial-Bus Data Rates of 100 Mbps, 200 Mbps, 400 Mbps, and 800 Mbps

• Physical Write Posting of up to Three Outstanding Transactions

• Serial ROM or Boot ROM Interface Supports 2-Wire Serial EEPROM Devices

• 33-MHz/32-Bit PCI Interface

• Multifunction Terminal MFUNC Terminal 1:

– PCI_CLKRUN Protocol Per PCI Mobile Design Guide

– General-Purpose I/O GPIO

– CYCLEIN/CYCLEOUT for External Cycle Timer Control for Customized Synchronization

• PCI Burst Transfers and Deep FIFOs to Tolerate Large Host Latency

– Transmit FIFO—5K Asynchronous

– Transmit FIFO—2K Isochronous

– Receive FIFO—2K Asynchronous

– Receive FIFO—2K Isochronous

• D0, D1, D2, and D3 Power States and PME Events Per PCI Bus Power Management Interface Specification

• Programmable Asynchronous Transmit Threshold

• Isochronous Receive Dual-Buffer Mode

• Out-of-Order Pipelining for Asynchronous Transmit Requests

• Initial-Bandwidth-Available and Initial-Channels-Available Registers

• Digital Video and Audio Performance Enhancements