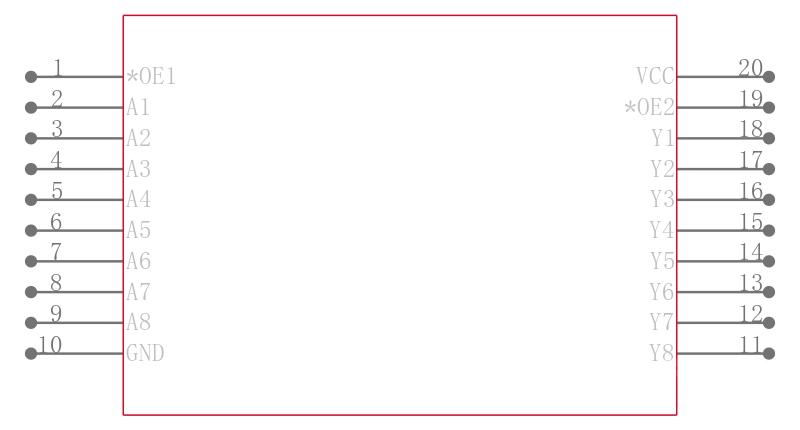

SN74LV541APW

八路缓冲器/驱动器,具有三态输出 OCTAL BUFFERS/DRIVERS WITH 3-STATE OUTPUTS

The is an octal Buffer/Driver with 3-state outputs and is designed for 2 to 5.5V VCC operation. This device is ideal for driving bus lines or buffer memory address registers. It features inputs and outputs to facilitate printed circuit board layout. The 3-state control gate is a two-input AND gate with active-low inputs so that if either output-enable input is high, all corresponding outputs are in the high-impedance state. The outputs provide non-inverted data when they are not in the high-impedance state. To ensure the high-impedance state during power up or power down, both OE should be tied to VCC through a pull-up resistor and the minimum value of the resistor is determined by the current-sinking capability of the driver The SN74LV541A device is fully specified for partial-power-down applications using IOFF. The IOFF circuitry disables the outputs, preventing damaging current backflow through the devices when it is powered down.

- .

- Support mixed-mode voltage operation on all ports

- .

- IOFF Supports partial-power-down mode operation

- .

- Latch-up performance exceeds 250mA per JESD 17

- .

- 6ns at 5V Propagation delay tpd

- .

- <0.8V at VCC = 3.3V, TA = 25°C VOLP output ground bounce

- .

- >2.3V at VCC = 3.3V, TA = 25°C VOHV output VOH undershoot

- .

- Green product and no Sb/Br