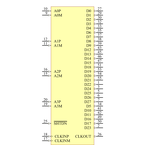

SN65LVDS94DGG

TEXAS INSTRUMENTS SN65LVDS94DGG SerDes, 串行/解串器, 1.904 Gbps, LVDS, LVTTL, TSSOP, 56 引脚

The is a LVDS SerDes Serializer/Deserializer Receiver contains four serial-in 7-bit parallel-out shift registers, a 7 x clock synthesizer and five low-voltage differential signalling LVDS line receivers in a single integrated circuit. These functions allow receipt of synchronous data from a compatible transmitter, such as the SN65LVDS93 and SN65LVDS95, over five balanced-pair conductors and expansion to 28 bits of single-ended LVTTL synchronous data at a lower transfer rate. When receiving, the high-speed LVDS data is received and loaded into registers at the rate seven times the LVDS input clock CLKIN. The data is then unloaded to a 28-bit wide LVTTL parallel bus at the CLKIN rate. A phase-locked loop clock synthesizer circuit generates a 7 x clock for internal clocking and an output clock for the expanded data. The SN65LVDS94 presents valid data on the rising edge of the output clock CLKOUT.

- .

- 4:28 Data channel expansion at up to 1.904 gigabits per second throughput

- .

- Suited for point-to-point subsystem communication with very low EMI

- .

- Rising clock edge triggered outputs

- .

- Bus pins tolerate 4kV HBM ESD

- .

- No external components required for PLL

- .

- Operates from a single 3.3V supply and 250mW typical

- .

- Consumes <1mW when disabled

- .

- 5V Tolerant SHTDN input

- .

- 20 to 65MHz Wide phase-lock input frequency range

- .

- Green product and no Sb/Br