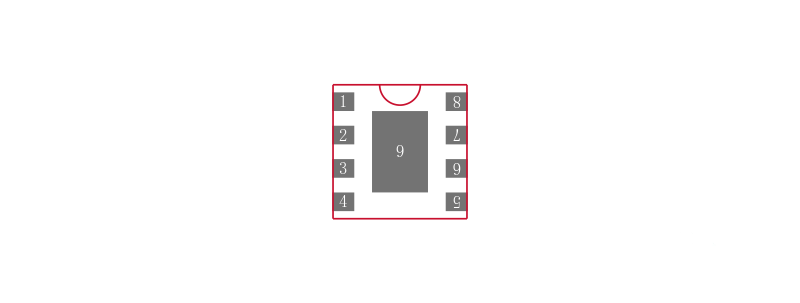

MC10EP51MNR4G

数据手册.pdf3.3V / 5V ECL D触发器与复位和差分时钟 3.3V / 5V ECL D Flip−Flop with Reset and Differential Clock

The MC10/100EP51 is a differential clock D flip-flop with reset. The device is functionally equivalent to the EL51 and LVEL51 devices.The reset input is an asynchronous, level triggered signal. Data enters the master portion of the flip-flop when the clock is LOW and is transferred to the slave, and thus the outputs, upon a positive transition of the clock. The differential clock inputs of the EP51 allow the device to be used as a negative edge triggered flip-flop.The differential input employs clamp circuitry to maintain stability under open input conditions. When left open, the CLK input will be pulled down to V and the CLKbar input will be biased at V

Features

---

|

- .

- 350ps Typical Propagation Delay

- .

- Maximum Frequency > 3 Ghz Typical

- .

- PECL Mode Operating Range: VCC = 3.0 V to 5.5 V with VEE = 0 V

- .

- NECL Mode Operating Range: VCC = 0 V with VEE = -3.0 V to -5.5 V

- .

- Open Input Default State

- .

- Safety Clamp on Inputs

- .

- Pb-Free Packages are Available