DSPIC33FJ64GS610-E/PF

数据手册.pdfMicrochip(微芯)

主动器件

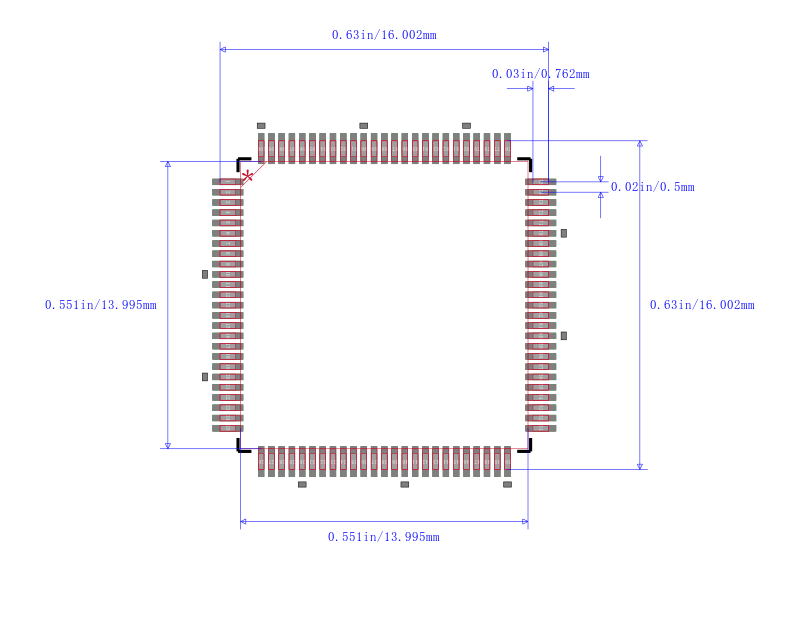

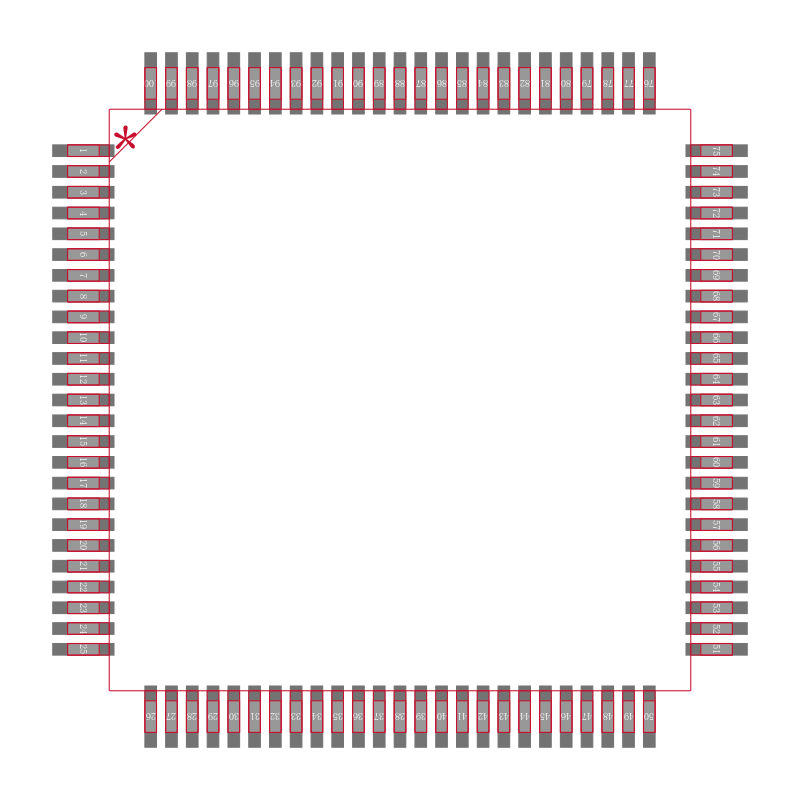

dsPIC33 系列 9 kB RAM 64 kB 闪存 16 位 数字 信号 控制器 - TQFP-100

Operating ConditionsdsPIC33F DSC CoreHigh-Speed PWMAdvanced Analog FeaturesTimers/Output Compare/Input CaptureCommunication InterfacesDirect Memory Access DMA- .

- 3.0V to 3.6V, -40ºC to +85ºC, DC to 50 MIPS 3.0V to 3.6V, -40ºC to +125ºC, DC to 40 MIPS Code-efficient C and Assembly architecture Two 40-bit wide accumulators Single-cycle MAC/MPY with dual data fetch Single-cycle mixed-sign MUL plus hardware divide 32-bit multiply support Up to nine PWM pairs with independent timing Dead time for rising and falling edges 1.04 ns PWM resolution PWM support for: DC/DC, AC/DC, Inverters, PFC, Lighting BLDC, PMSM, ACIM, SRM Programmable Fault inputs Flexible trigger configurations for ADC conversions High-Speed ADC module: 10-bit resolution with up to two Successive Approximation Register SAR converters up to 4 Msps Up to four High-Speed Comparators with direct connection to the PWM module: 10-bit Digital-to-Analog Converter DAC for each comparator DAC reference output Six general purpose timers: Five 16-bit and up to two 32-bit timers/counters Four Output Compare OC modules configurable as timers/counters Quadrature Encoder Interface QEI module configurable as timer/counter Four Input Capture IC modules Two UART modules 12.5 Mbps With support for LIN 2.0 protocols and IrDA® Two 4-wire SPI modules 15 Mbps ECAN™ module 1 Mbaud CAN 2.0B support Two I2C™ modules up to 1 Mbaud with SMBus Support PPS to allow function remap Programmable Cyclic Redundancy Check CRC 4-channel DMA with user-selectable priority arbitration UART, SPI, ECAN™, IC, OC, and Timers