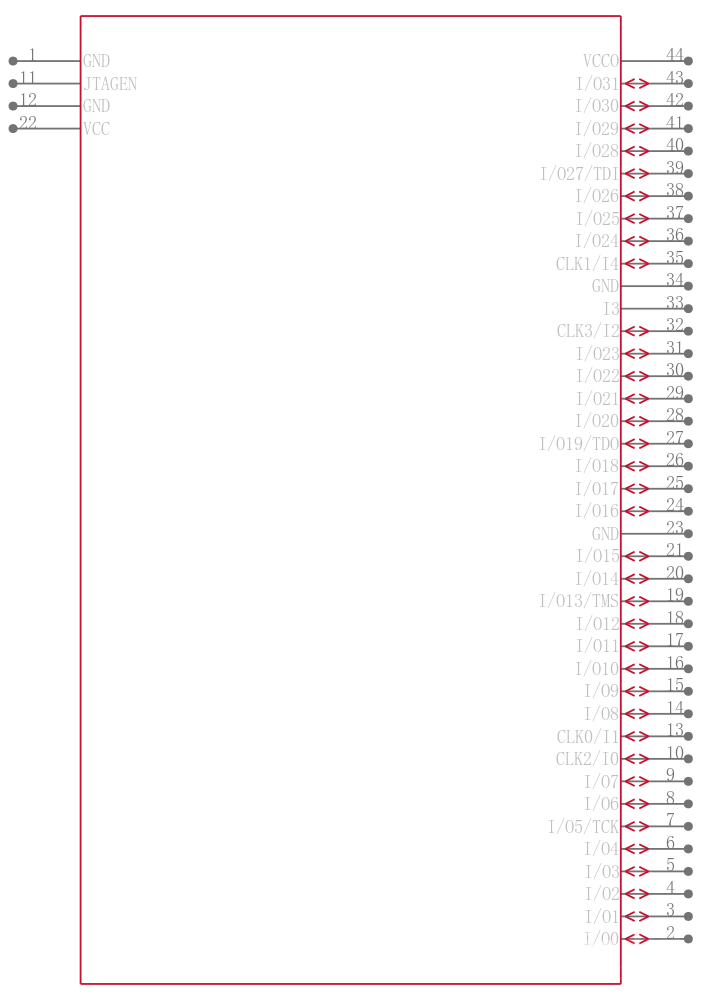

CY37064P44-200JXC

5V , 3.3V , ISRTM高性能的CPLD 5V, 3.3V, ISRTM High-Performance CPLDs

General Description

The Ultra37000™ family of CMOSCPLDs provides a range of high-density programmable logic solutions with unparalleled system performance. The Ultra37000 family is designed to bring the flexibility, ease of use, and performance of the 22V10 to high-density CPLDs. The architecture is based on a number of logic blocks that are connected by a Programmable Interconnect Matrix PIM.

Features

• In-System Reprogrammable™ ISR™ CMOS CPLDs

— JTAG interface for reconfigurability

— Design changes do not cause pinout changes

— Design changes do not cause timing changes

• High density

— 32 to 512 macrocells

— 32 to 264 I/O pins

— Five dedicated inputs including four clock pins

• Simple timing model

— No fanout delays

— No expander delays

— No dedicated vs. I/O pin delays

— No additional delay through PIM

— No penalty for using full 16 product terms

— No delay for steering or sharing product terms

• 3.3V and 5V versions

• PCI-compatible[1]

• Programmable bus-hold capabilities on all I/Os

• Intelligent product term allocator provides:

— 0 to 16 product terms to any macrocell

— Product term steering onan individual basis

— Product term sharing among local macrocells

• Flexible clocking

— Four synchronous clocks per device

— Product term clocking

— Clock polarity control per logic block

• Consistent package/pinout offering across all densities

— Simplifies design migration

— Same pinout for 3.3V and 5.0V devices

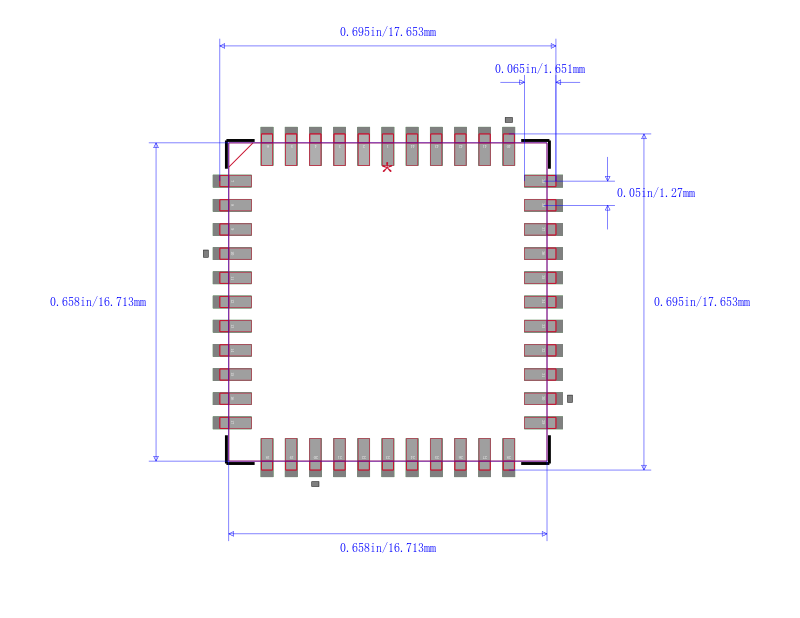

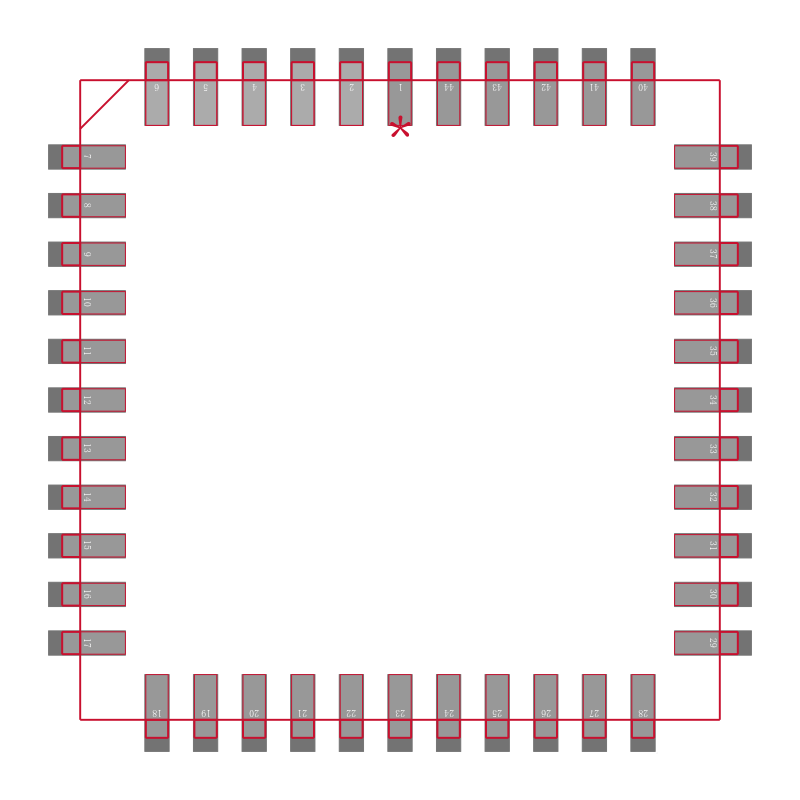

• Packages

— 44 to 400 leads in PLCC, CLCC, PQFP, TQFP, CQFP, BGA, and Fine-Pitch BGA packages

— LeadPb-free packages available