ADRF6821ACPZ-RL7

数据手册.pdfDPD RFIC with Integrated Fractional-N PLL and VCO 56Pin LFCSP EP T/R

Product Details

The ADRF6821 is a highly integrated, dual radio frequency RF input, zero intermediate frequency IF/low IF RFIC receiver with a quadrature demodulator, digital step attenuator DSA, IF linear amplifiers, an integrated, fractional-N phase-locked loop PLL, and a low phase noise, multicore, voltage controlled oscillator VCO. The RFIC is ideally suited for communication digital predistortion DPD systems.

The high isolation 2:1 RF switch and on-chip wideband RF balun enable the ADRF6821 to support two single-ended, 50 Ω terminated RF inputs. A programmable attenuator ensures an optimal differential RF input level to the high linearity demodulator core. The integrated attenuator offers an attenuation range of 15 dB with a step size of 1 dB. High linearity IF amplifiers follow the demodulator and provide an interface to the next component in the chain, typically an analog-to-digital converter ADC.

The ADRF6821 offers two alternatives for generating the differential local oscillator LO input signal: internally via the on-chip fractional-N synthesizer with low phase noise VCOs or externally via a low phase noise LO signal. The integrated synthesizer enables continuous LO coverage from 450 MHz to 2800 MHz. The PLL reference input supports a wide frequency range and includes integrated reference dividers before the phase frequency detector PFD.

When selected, the output of the internal fractional-N synthesizer is applied to a divide by 2, quadrature phase splitter. From the external LO path, a 2× LO signal can be used with the divide by 2, quadrature phase splitter to generate the quadrature LO inputs to the mixers.

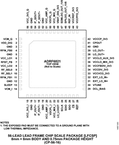

The ADRF6821 is fabricated using an advanced silicon germanium SiGe, bipolar complementary metal oxide semiconductor BiCMOS process. It is available in a 56-lead, RoHS compliant, 8 mm × 8 mm LFCSP package with an exposed pad. Performance is specified over the −40°C to +105°C case temperature range.

**Applications**

- .

- Cellular W-CDMA/GSM/LTE

- .

- DPD receivers

- .

- Microwave, point to point radios

### Features and Benefits

- .

- DPD receiver with integrated fractional-N PLL

- .

- RF input frequency range: 450 MHz to 2800 MHz

- .

- Internal LO input frequency range: 450 MHz to 2800 MHz

- .

- Dual RF inputs with SPDT absorptive RF switches

- .

- Integrated RF balun for single-ended 50 Ω input

- .

- Integrated VCO to cover complete RF input range

- .

- Digital programmable LO phase offset and dc nulling

- .

- Programmable via 4-wire SPI

- .

- 56-lead, 8 mm × 8 mm LFCSP