AD9518-4BCPZ-REEL7

数据手册.pdf6-Output Clock Generator with Integrated 1.6GHz VCO

Product Details

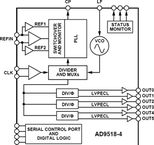

The AD9518-41 The AD9518-41 provides a multi-output clock distribution function with subpicosecond jitter performance, along with an on-chip PLL and VCO. The on-chip VCO tunes from 1.45 GHz to 1.80 GHz. Optionally, an external VCO/VCXO of up to 2.4 GHz can be used.

The AD9518-4 emphasizes low jitter and phase noise to maximize data converter performance, and it can benefit other applications with demanding phase noise and jitter requirements.

The AD9518-4 features six LVPECL outputs in three pairs. The LVPECL outputs operate to 1.6 GHz.

For applications that require additional outputs, a crystal reference input, zero-delay, or EEPROM for automatic configuration at startup, the AD9520 and AD9522 are available.

In addition, the AD9516 and AD9517 are similar to the AD9518 but have a different combination of outputs.

Each pair of outputs has dividers that allow both the divide ratio and coarse delay or phase to be set. The range of division for the LVPECL outputs is 1 to 32.

The AD9518-4 is available in a 48-lead LFCSP and can be operated from a single 3.3 V supply. An external VCO, which requires an extended voltage range, can be accommodated by connecting the charge pump supply VCP to 5 V. A separate LVPECL power supply can be from 2.5 V to 3.3 V nominal.

The AD9518-4 is specified for operation over the industrial range of −40°C to +85°C.

**Applications**

- .

- Low jitter, low phase noise clock distribution

- .

- 10/40/100 Gb/sec networking line cards, including SONET, Synchronous Ethernet, OTU2/3/4

- .

- Forward error correction G.710

- .

- Clocking high speed ADCs, DACs, DDSs, DDCs, DUCs, MxFEs

- .

- High performance wireless transceivers

- .

- ATE and high performance instrumentation

1AD9518 is used throughout the data sheet to refer to all the members of the AD9518 family. However, when AD9518-4 is used, it refers to that specific member of the AD9518 family.

### Features and Benefits

- .

- Low phase noise, phase-locked loop PLL

For more information please refer to the data sheet

- .

- 3 pairs of 1.6 GHz LVPECL outputs

Each output pair shares a 1-to-32 divider with coarse phase delay

Additive output jitter: 225 fs rms

Channel-to-channel skew paired outputs of <10 ps

- .

- Automatic synchronization of all outputs on power-up

- .

- Manual output synchronization available

- .

- Available in a 48-lead LFCSP