ADSP-2187NBSTZ-320

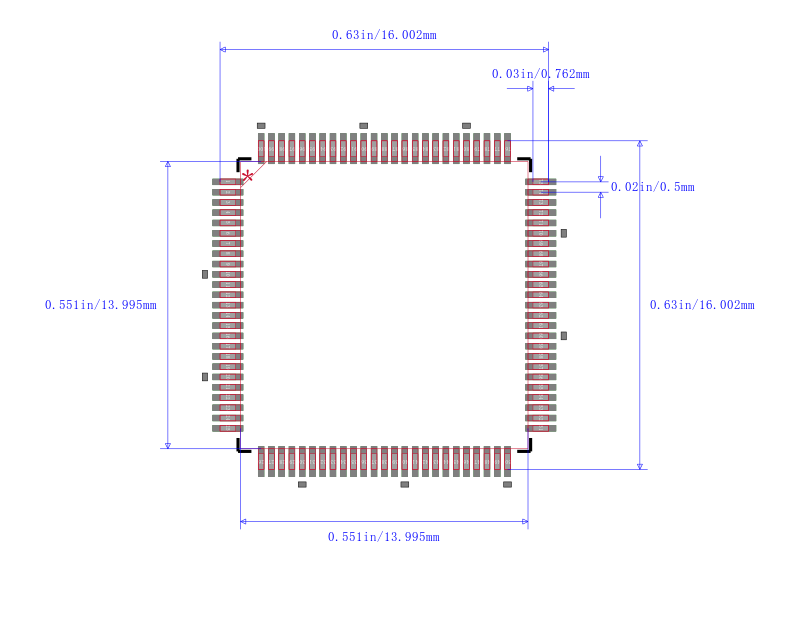

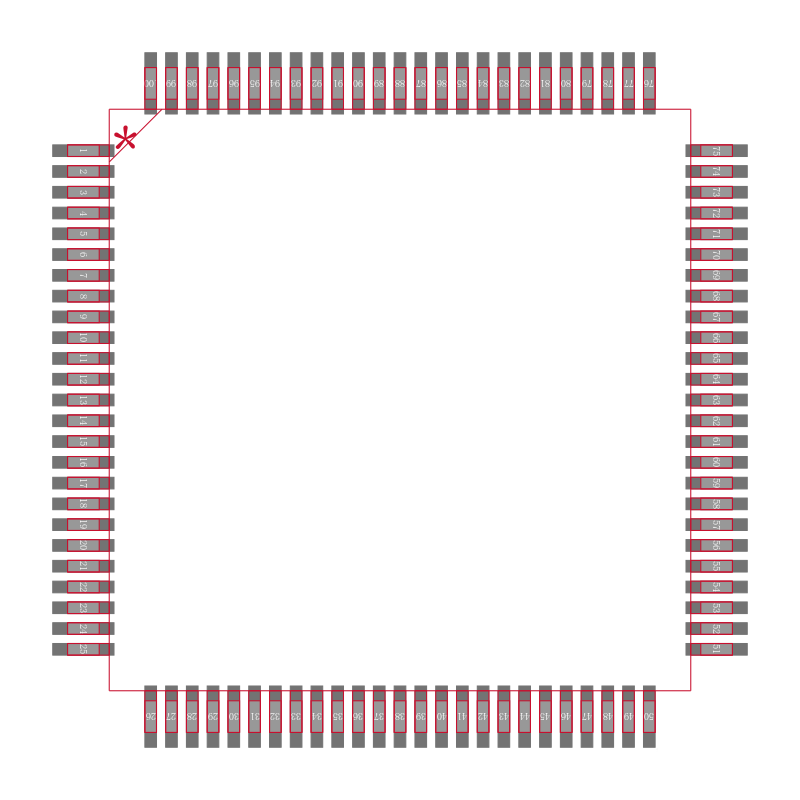

数据手册.pdfANALOG DEVICES ADSP-2187NBSTZ-320 芯片, 数字信号处理器, 浮点, 16位, 80MHZ, LQFP-100

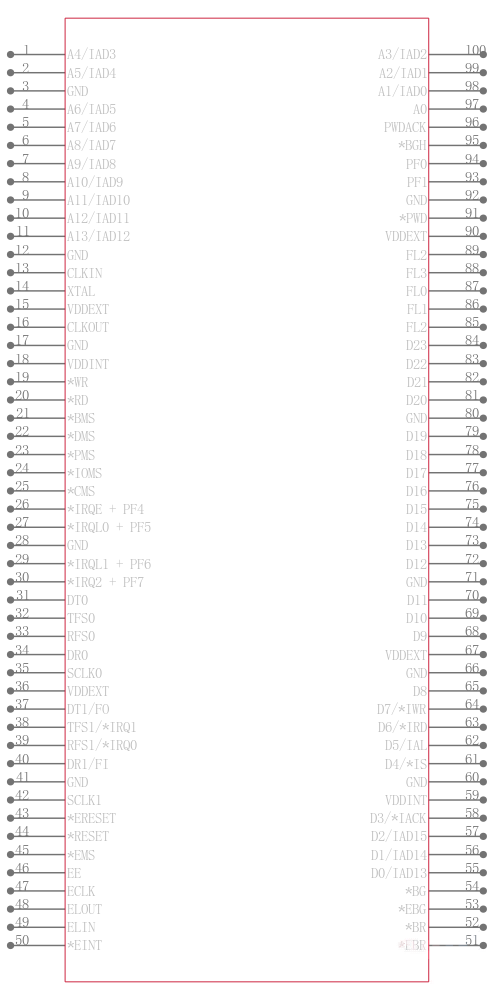

The is a single-chip Digital Signal Processing Microcomputer is pin-compatible and is differentiated solely by the amount of on-chip SRAM. This feature, combined with ADSP-21xx code compatibility, provides a great deal of flexibility in the design decision. ADSP-2187N series members combine the ADSP-2100 family base architecture three computational units, data address generators and a program sequencer with two serial ports, a 16-bit internal DMA port, a byte DMA port, a programmable timer, Flag I/O, extensive interrupt capabilities and on-chip program and data memory. ADSP-2187N series members integrate up to 256K bytes of on-chip memory configured as up to 48K words 24-bit of program RAM and up to 56K words 16-bit of data RAM. Power down circuitry is also provided to meet the low power needs of battery-operated portable equipment.

- .

- Single-cycle instruction execution

- .

- Single-cycle context switch

- .

- Low CMOS standby power dissipation with 200 CLKIN cycle recoveries from power-down condition

- .

- Low power dissipation in idle mode

- .

- Up to 48K words program memory RAM

- .

- Up to 56K words data memory RAM

- .

- Dual-purpose program memory for both instruction and data storage

- .

- Two independent data address generators

- .

- Powerful program sequencer provides zero overhead looping conditional instruction execution

- .

- Programmable 16-bit interval timer with pre-scalar

- .

- 80MHz Instruction rate

- .

- 12.5ns Instruction cycle time at 1.8V internal

- .

- 80 MIPS sustained performance

- .

- 3-bus Architecture allows dual operand fetches in every instruction cycle