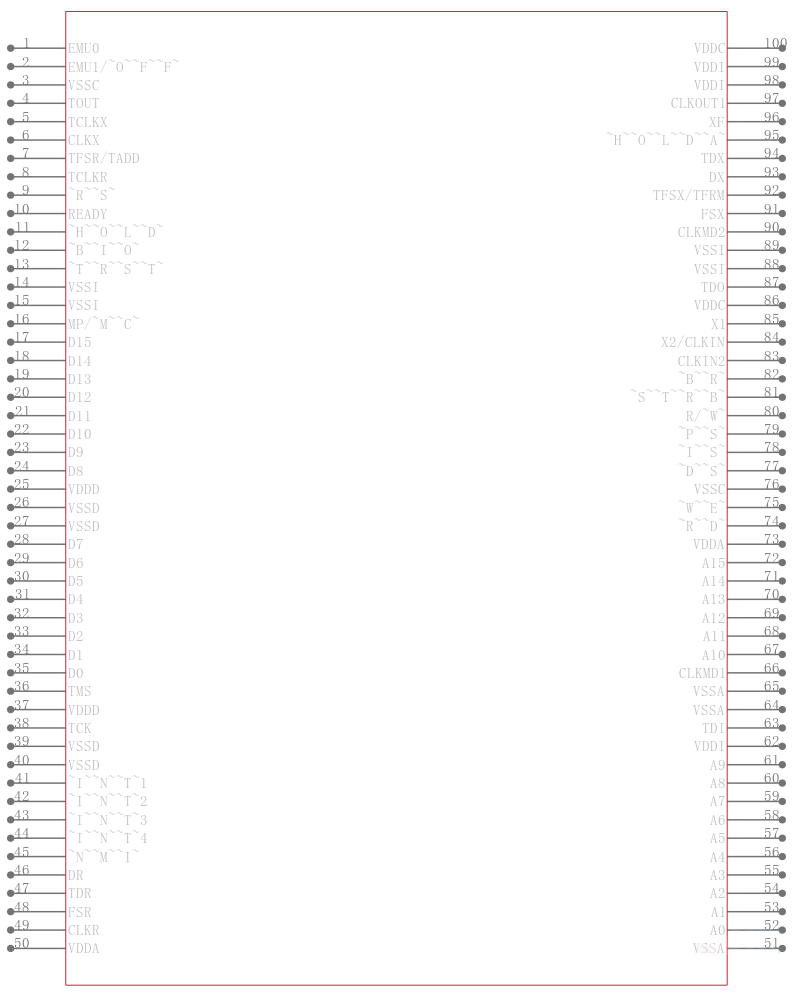

TMS320LBC51PZA57

数字信号处理器 DIGITAL SIGNAL PROCESSORS

description

The TMS320C5x generation of the Texas Instruments ™ TMS320 digital signal processors DSPs is fabricated with static CMOS integrated circuit technology; the architectural design is based upon that of an earlier TI DSP, the TMS320C25. The combination of advanced Harvard architecture, on-chip peripherals, on-chip memory, and a highly specialized instruction set is the basis of the operational flexibility and speed of the ’C5x‡ devices. They execute up to 50 million instructions per second MIPS.

• Powerful 16-Bit TMS320C5x CPU

• 20-, 25-, 35-, and 50-ns Single-Cycle Instruction Execution Time for 5-V Operation

• 25-, 40-, and 50-ns Single-Cycle Instruction Execution Time for 3-V Operation

• Single-Cycle 16 × 16-Bit Multiply/Add

• 224K × 16-Bit Maximum Addressable External Memory Space 64K Program, 64K Data, 64K I/O, and 32K Global

• 2K, 4K, 8K, 16K, 32K × 16-Bit Single-Access On-Chip Program ROM

• 1K, 3K, 6K, 9K × 16-Bit Single-Access On-Chip Program/Data RAM SARAM

• 1K Dual-Access On-Chip Program/Data RAM DARAM

• Full-Duplex Synchronous Serial Port for Coder/Decoder Interface

• Time-Division-Multiplexed TDM Serial Port

• Hardware or Software Wait-State Generation Capability

• On-Chip Timer for Control Operations

• Repeat Instructions for Efficient Use of Program Space

• Buffered Serial Port

• Host Port Interface

• Multiple Phase-Locked Loop PLL Clocking Options ×1, ×2, ×3, ×4, ×5, ×9 Depending on Device

• Block Moves for Data/Program Management

• On-Chip Scan-Based Emulation Logic

• Boundary Scan

• Five Packaging Options

– 100-Pin Quad Flat Package PJ Suffix

– 100-Pin Thin Quad Flat Package PZ Suffix

– 128-Pin Thin Quad Flat Package PBK Suffix

– 132-Pin Quad Flat Package PQ Suffix

– 144-Pin Thin Quad Flat Package PGE Suffix

• Low Power Dissipation and Power-Down Modes:

– 47 mA 2.35 mA/MIP at 5 V, 40-MHz Clock Average

– 23 mA 1.15 mA/MIP at 3 V, 40-MHz Clock Average

– 10 mA at 5 V, 40-MHz Clock IDLE1 Mode

– 3 mA at 5 V, 40-MHz Clock IDLE2 Mode

– 5 µA at 5 V, Clocks Off IDLE2 Mode

• High-Performance Static CMOS Technology

• IEEE Standard 1149.1† Test-Access Port JTAG