SI53112-EK

数据手册.pdfSi53112、12 输出 PCIe 时钟缓冲器,Silicon LaboratoriesSilicon Laboratories 的 Si53112-EK 是 PCIe 时钟和开发套件,可提供每瓦特高性能,用于符合 PCI Express® Gen1/2/3 标准所需的时钟应用。 这些时钟生成器和缓冲器功率低两倍,并且能够提供高达 50% 的余量,符合 PCI-Express 抖动规格。 Silicon Labs Si53112-EK PCIe 时钟生成器和缓冲器完全集成端接电阻器、降低 BOM 成本、板空间要求和设计复杂性。 Si53112 是低功率、12 输出差分时钟缓冲器,满足 Intel DB1200ZL 规格的所有性能要求。 十二个 0.7 V 低功率、推挽式 HCSL 兼容 PCIe Gen 3 输出 单独 OE HW 引脚,用于每个输出时钟 100 MHz /133 MHz PLL 操作,支持 PCIe 和 QPI PLL 带宽 SW SMBUS 编程覆盖 HW 引脚的闭锁值 9 个 SMBUS 地址 配置 SMBus 地址,以在单控制网络 3.3 V 电源电压操作中允许多个缓冲器 PLL 或旁路模式 容许展频 1.05 至 3.3 V 输入/输出电源电压 50 ps 输出到输出偏斜 50 ps cyc-cyc 抖动(PLL 模式) 低相位抖动(符合 Intel® QPI、PCIe Gen 1/Gen 2/Gen 3) 100 ps 输入到输出延时 广泛的温度范围:–40 到 85 °C 封装:64 引脚 QFN ### 时钟发生器/缓冲器

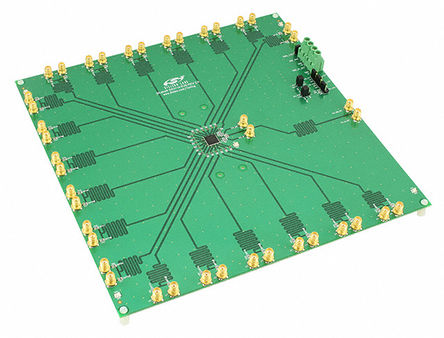

评估板,用于 Si53112、12 输出 PCIe 时钟缓冲器,Silicon Laboratories

Silicon Laboratories 的 Si53112-EK 是 PCIe 时钟和开发套件,可提供每瓦特高性能,用于符合 PCI Express® Gen1/2/3 标准所需的时钟应用。 这些时钟生成器和缓冲器功率低两倍,并且能够提供高达 50% 的余量,符合 PCI-Express 抖动规格。 Si53112-EK PCIe 时钟生成器和缓冲器完全集成端接电阻器、降低 BOM 成本、板空间要求和设计复杂性。

Si53112 是低功率、12 输出差分时钟缓冲器,满足 Intel DB1200ZL 规格的所有性能要求。

十二个 0.7 V 低功率、推挽式 HCSL 兼容 PCIe Gen 3 输出

单独 OE HW 引脚,用于每个输出时钟

100 MHz /133 MHz PLL 操作,支持 PCIe 和 QPI

PLL 带宽 SW SMBUS 编程覆盖 HW 引脚的闭锁值

9 个 SMBUS 地址

配置 SMBus 地址,以在单控制网络 3.3 V 电源电压操作中允许多个缓冲器

PLL 或旁路模式

容许展频

1.05 至 3.3 V 输入/输出电源电压

50 ps 输出到输出偏斜

50 ps cyc-cyc 抖动(PLL 模式)

低相位抖动(符合 Intel® QPI、PCIe Gen 1/Gen 2/Gen 3)

100 ps 输入到输出延时

广泛的温度范围:–40 到 85 °C

封装:64 引脚 QFN