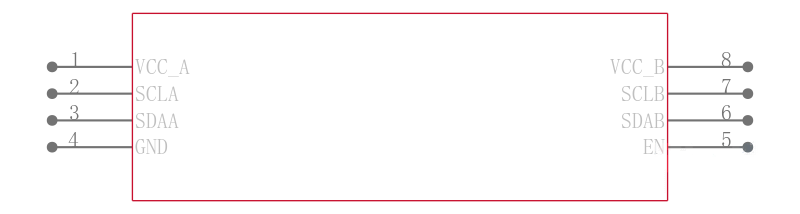

PCA9517ADP

数据手册.pdf电平转换I2C总线中继器 Level translating I2C-bus repeater

The is a CMOS Integrated Circuit that provides level shifting between low voltage down to 0.9V and higher voltage 2.7V to 5.5V I²C-bus or SMBus applications. While retaining all the operating modes and features of the I²C-bus system during the level shifts, it also permits extension of the I²C-bus by providing bidirectional buffering for both the data SDA and the clock SCL lines, thus enabling two buses of 400pF. Using the PCA9517A enables the system designer to isolate two halves of a bus for both voltage and capacitance. The SDA and SCL pins are overvoltage tolerant and are high-impedance when the PCA9517A is unpowered. The 2.7V to 5.5V bus port B drivers behave much like the drivers on the PCA9515A device, while the adjustable voltage bus port A drivers drive more current and eliminate the static offset voltage. This results in a low on the port B translating into a nearly 0V low on the port A which accommodates smaller voltage swings of lower voltage logic.

- .

- 2-channel Bidirectional buffer isolates capacitance and allows 400pF on either side of device

- .

- I²C-bus and SMBus compatible

- .

- Active high repeater enable input

- .

- Open-drain input/outputs

- .

- Lock-up free operation

- .

- Supports arbitration and clock stretching across repeater

- .

- Accommodates Standard-mode and Fast-mode I²C-bus devices and multiple masters

- .

- Powered-off high-impedance I²C-bus pins

- .

- 5V tolerant I²C-bus and enable pins

- .

- Latch-up testing is done to JEDEC standard JESD78 that exceeds 100mA

ESD sensitive device, take proper precaution while handling the device.