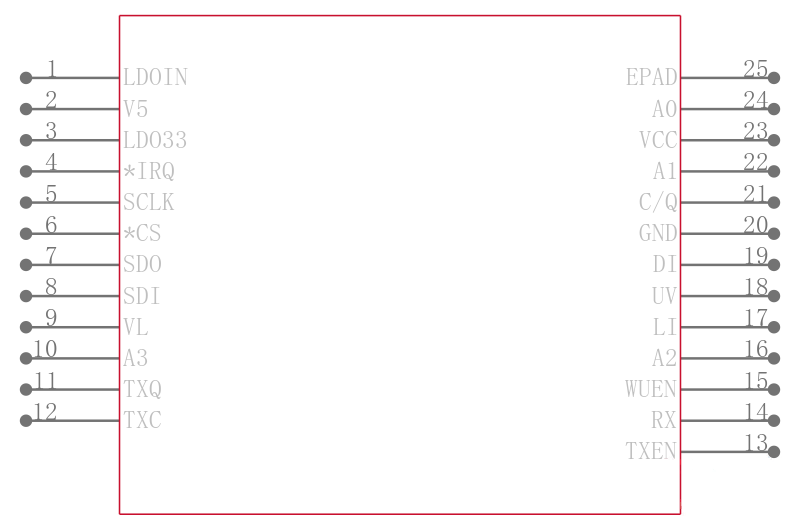

MAX14824GTG+

数据手册.pdfIO- Link主站收发器 IO-Link Master Transceiver

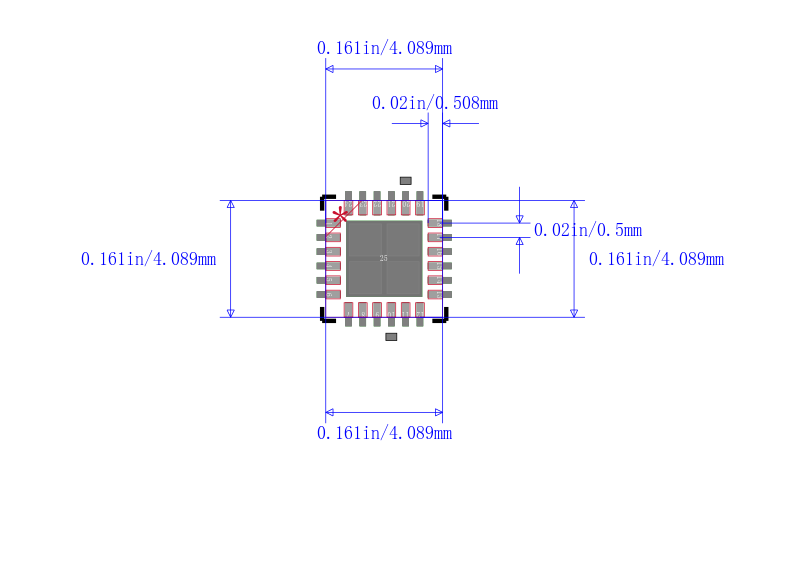

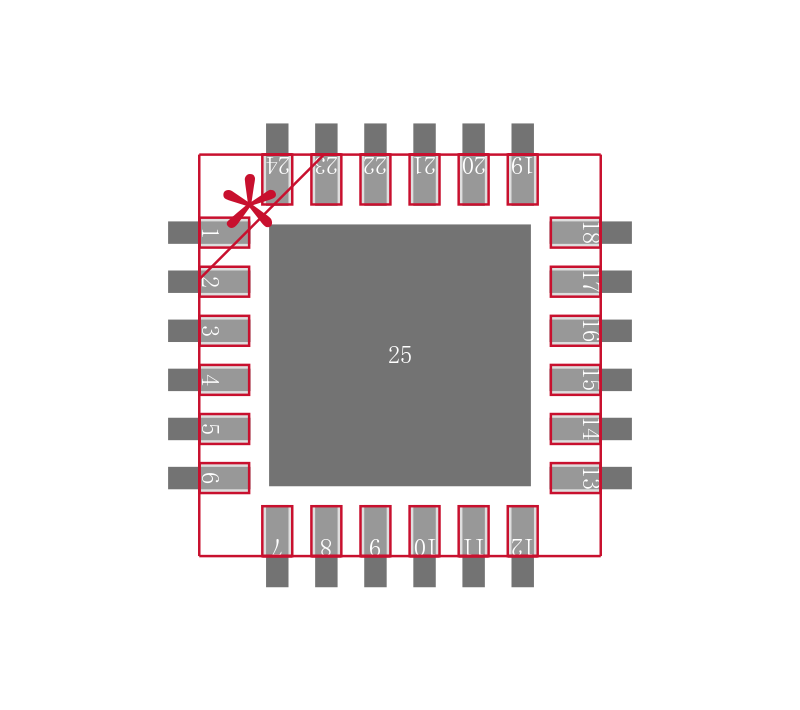

The is an IO-link master transceiver in 24 pin TQFN package. The IO-Link master interface that integrates an IO-Link physical layer transceiver with an auxiliary digital input and two linear regulators. High port count IO-Link master applications are supported through in-band SPI addressing and the 12MHz SPI interface minimizes host controller access times. In-band addressing and selectable SPI addresses enable cascading up to 16 devices. The device supports all the IO-Link data rates and features slew-rate-controlled drivers to reduce EMI. The driver drives up to 300mA min load current. Internal wake-up circuitry automatically determines the correct wake-up polarity allowing for the use of simple UARTs for wake-up pulse generation. Typical applications include IO-link master controllers, PLC field-bus gateways, high port count IO-link masters and 24V digital inputs and outputs.

- .

- Supply voltage range is 9V to 36V

- .

- Operating temperature range from -40°C to 105°C

- .

- IO link v.1.0 and v.1.1 physical layer compliant

- .

- Supports COM1, COM2 and COM3 data rates

- .

- Push-pull, high-side or low-side outputs

- .

- 1µF C/Q load drive capability

- .

- Generates 500mA wake-up pulse

- .

- Automatic wake-up pulse polarity

- .

- 5V and 3.3V linear regulators

- .

- SPI interface for configuration and monitoring and SPI based chip addressing