AD6688BBPZRL-3000

数据手册.pdfRF Diversity and 1.2GHz BW Observation Receiver

Product Details

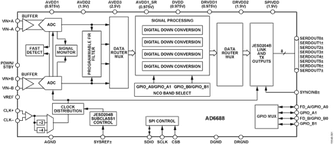

The AD6688 is a 1.2 GHz bandwidth, mixed-signal, direct radio frequency RF sampling receiver. It consists of two 14-bit, 3.0 GSPS analog-to-digital converters ADCs and various digital signal processing blocks consisting of four wideband digital downconverters DDCs. The AD6688 has an on-chip buffer and a sample-and-hold circuit designed for low power, small size, and ease of use. This product is designed to support communications applications capable of direct sampling wide bandwidth analog signals of up to 5 GHz. The 3 dB bandwidth of the ADC input is greater than 9 GHz. The AD6688 is optimized for wide input bandwidth, high sampling rate, excellent linearity, and low power in a small package.

The dual ADC cores feature a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth inputs supporting a variety of user-selectable input ranges. An integrated voltage reference eases design considerations. The analog input and clock signals are differential inputs. The ADC data outputs are internally connected to four DDCs through a crossbar mux. Each DDC consists of up to five cascaded signal processing stages: a 48-bit numerically controlled oscillator NCO and up to four half-band decimation filters. The NCO has the option to select preset bands over the general-purpose input/output GPIO pins, which enables selection of up to three bands. Operation of the AD6688 between the DDC modes is selectable via SPI-programmable profiles.

In addition to the DDC blocks, the AD6688 has several functions that simplify the automatic gain control AGC function in a communications receiver. The programmable threshold detector allows monitoring of the incoming signal power using the fast detect control bits in Register 0x0245 of the ADC. If the input signal level exceeds the programmable threshold, the fast detect indicator goes high. Because this threshold indicator has low latency, the user can quickly turn down the system gain to avoid an overrange condition at the ADC input. Besides the fast detect outputs, the AD6688 also offers signal monitoring capability. The signal monitoring block provides additional information about the signal being digitized by the ADC.

The user can configure the Subclass 1 JESD204B-based high speed serialized output in a variety of one-lane, two-lane, four-lane, six-lane, and eight-lane configurations, depending on the DDC configuration and the acceptable lane rate of the receiving logic device. Multidevice synchronization is supported through the SYSREF± and SYNCINB± input pins.

The AD6688 has flexible power-down options that allow significant power savings when desired. All of these features can be programmed using a 3-wire serial port interface SPI.

The AD6688 is available in a Pb-free, 196-ball BGA specified over the −40°C to +85°C ambient temperature range.

**Product Highlights**

1. Wide full power bandwidth supports IF sampling of signals up to 9GHz -3dB point.

2. Four Integrated wide-band decimation filter and NCO blocks supporting multi-band receivers.

3. Fast NCO switching enabled through GPIO pins.

4. Flexible SPI interface controls various product features and functions to meet specific system requirements.

5. Programmable fast overrange detection and signal monitoring.

6. On-chip temperature dioide for system thermal management.

7. 12mm x 12mm 196-Lead BGA

**Applications**

- .

- Diversity multiband, multimode digital receivers

- .

- 3G/4G, TD-SCDMA, W-CDMA, GSM, LTE, LTE-A

- .

- DOCSIS 3.0 CMTS upstream receive paths

- .

- HFC digital reverse path receivers

### Features and Benefits

- .

- JESD204B Subclass 1 coded serial digital outputs

- .

- Support for lane rates up to 16 Gbps per lane

- .

- 1.7 W total power per channel at 3 GSPS default settings

- .

- Performance at −2 dBFS amplitude, 2.6 GHz input

- .

- SFDR = 70 dBFS

- .

- NSD = −148.0 dBFS/Hz

- .

- Performance at −9 dBFS amplitude, 2.6 GHz input

- .

- SFDR = 75 dBFS

- .

- NSD = −151.4 dBFS/Hz

- .

- Integrated input buffer

- .

- Noise density = −152.0 dBFS/Hz

- .

- 0.975 V, 1.9 V, and 2.5 V dc supply operation

- .

- 9 GHz analog input full power bandwidth −3 dB

- .

- Amplitude detect bits for efficient AGC implementation

- .

- Two Integrated wideband digital processors per channel

- .

- 48-bit NCO

- .

- 4 cascaded half band filters

- .

- Phase coherent NCO switching

- .

- Up to 4 channels available

- .

- Serial port control

- .

- Integer clock divide by 2 and divide by 4

- .

- Flexible JESD204B lane configurations

- .

- On-chip dither