AD7714YRUZ-REEL7

数据手册.pdf3V/5V,CMOS,500μA,24位Σ-Δ型信号调理ADC

Product Details

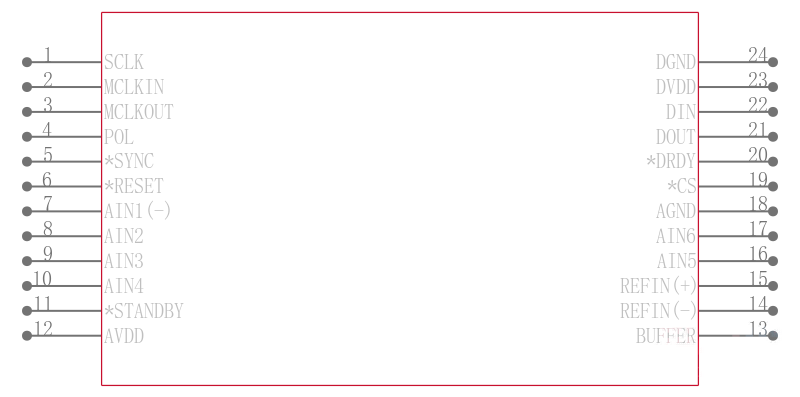

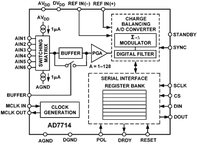

The AD7714 is a complete analog front end for low-frequency measurement applications. The device accepts low level signals directly from a transducer and outputs a serial digital word. It employs a sigma-delta conversion technique to realize up to 24 bits of no missing codes performance. The input signal is applied to a proprietary programmable gain front end based around an analog modulator. The modulator output is processed by an on-chip digital filter. The first notch of this digital filter can be programmed via the on-chip control register allowing adjustment of the filter cutoff and settling time.

The part features three differential analog inputs which can also be configured as five pseudo-differential analog inputs as well as a differential reference input. The AD7714 thus performs all signal conditioning and conversion for a system consisting of up to five channels. A new Y grade has recently been added to the existing range. Compared to the A grades this new grade has an extended operating temperature range, schmitt trigger inputs on SCLK and DIN, tighter linearity specifications, lower power consumption and is available in a smaller package.

The AD7714 is ideal for use in smart microcontroller- or DSP-based systems. It features a serial interface that can be configured for three-wire operation. Gain settings, signal polarity and channel selection can be configured in software using the serial port. The AD7714 provides self-calibration, system calibration and background calibration options and also allows the user to read and write the on-chip calibration registers.

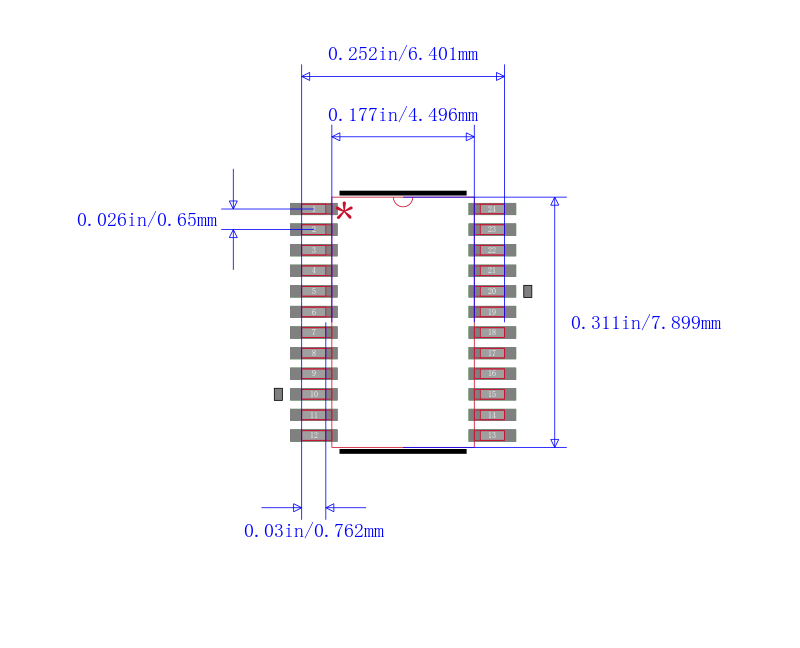

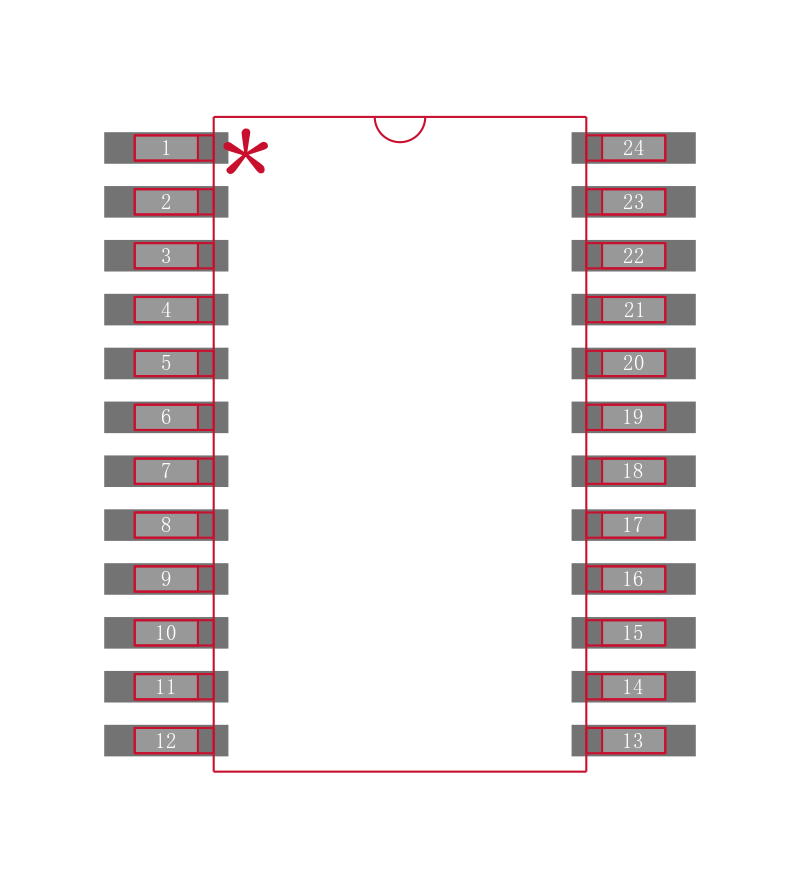

CMOS construction ensures very low power dissipation, and the power-down mode reduces the standby power consumption to 15 µW typical at 3 V. Minimum operating voltage for the A grades is 3 V and 2.7 V for the Y grades. The A grades are available in a 24-pin, 0.3 inch-wide, plastic dual-in-line package DIP; a 24 lead small outline SOIC package and a 28-lead shrink small outline package SSOP. The new Y grade is available in a 24-pin, 0.3 inch-wide, plastic dual-in-line package DIP; a 24 lead small outline SOIC package and a 24-lead Thin Shrink Small Outline Package TSSOP.

### Features and Benefits

- .

- Charge Balancing ADC

24 Bits No Missing Codes

0.0015% Nonlinearity

- .

- Five-Channel Programmable Gain Front End

Gains from 1 to 128

Can Be Configured as Three Fully Differential

Inputs or Five Pseudo-Differential Inputs

- .

- Three-Wire Serial Interface

SPI®, QSPI™, MICROWIRE™ and DSP Compatible

- .

- 3 V AD7714-3 or 5 V AD7714-5 Operation

- .

- Low Current 350 µA typ with Power-Down 5 µA typ

- .

- Low Noise <150 nV rms

- .

- Low-Pass Filter with Programmable Filter Cutoffs

- .

- Please see data sheet for additional features