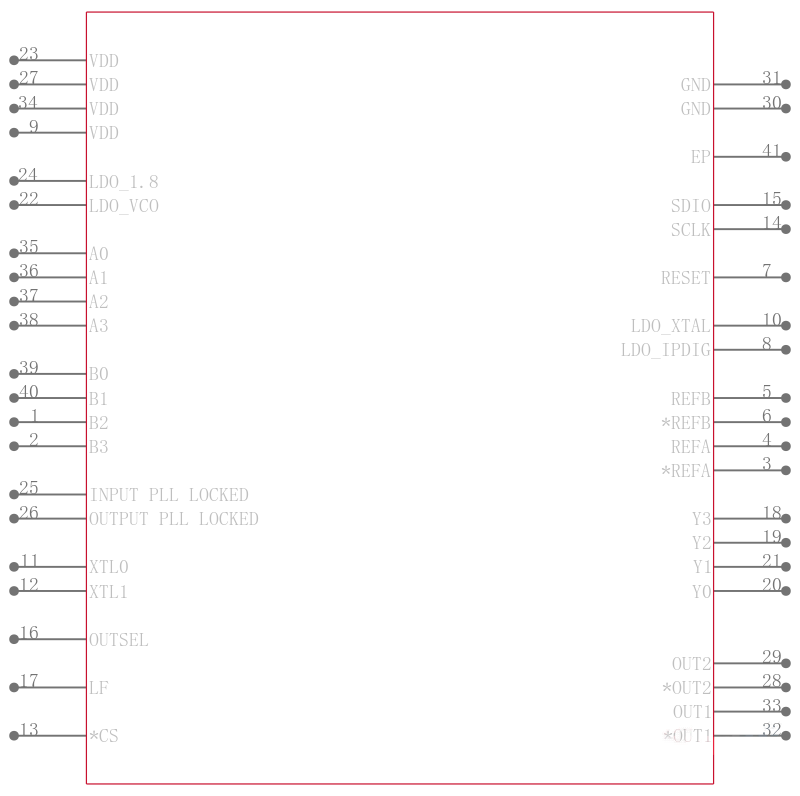

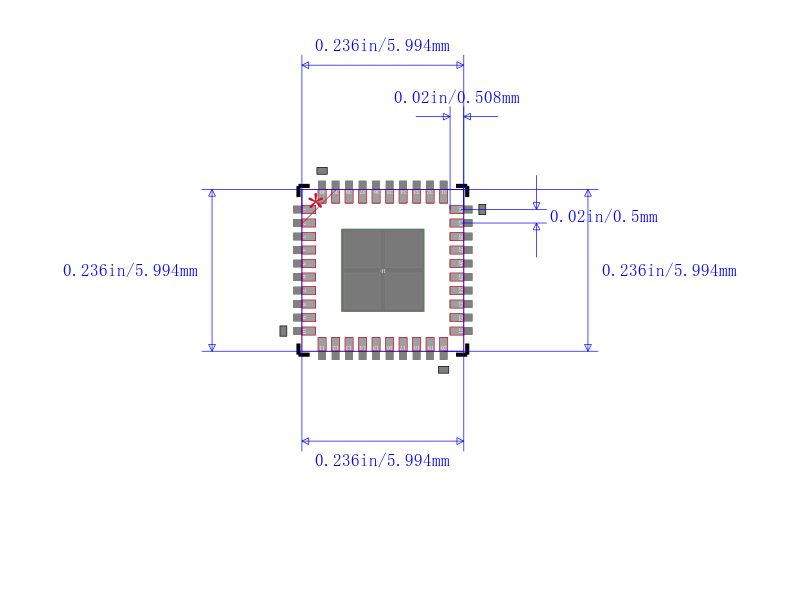

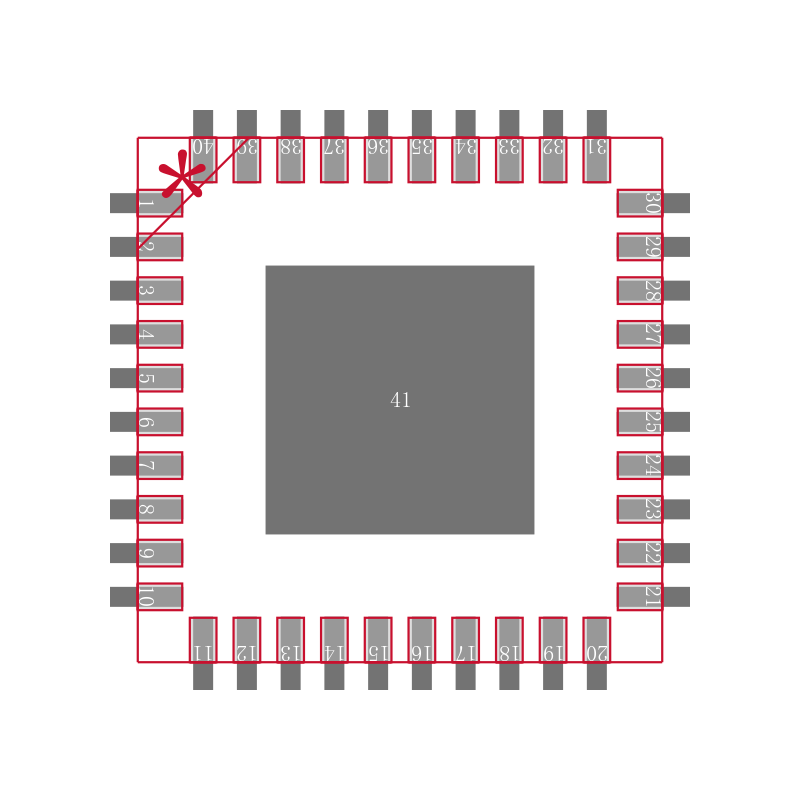

AD9551BCPZ

数据手册.pdf多时钟发生器 Multiservice Clock Generator

Product Details

The AD9551 accepts one or two reference input signals to synthe-size one or two output signals. The AD9551 uses a fractional-N PLL that precisely translates the reference frequency to the desired output frequency. The input receivers and output drivers provide both single-ended and differential operation.

Reference conditioning and switchover circuitry internally synchronizes the two references so that if one reference fails, there is virtually no phase perturbation at the output.

The AD9551 uses an external crystal and an internal DCXO to provide for holdover operation. If both references fail, the device maintains a steady output signal.

The AD9551 provides pin-selectable, preset divider values for standard and FEC adjusted network frequencies. The pin-selectable frequencies include any combination of 15 possible input frequencies and 16 possible output frequencies. A SPI interface provides further flexibility by making it possible to program almost any rational input/output frequency ratio.

The AD9551 is a clock generator that employs fractional-N-based phase-locked loops PLL using sigma-delta Σ-Δ modulators SDMs. The fractional frequency synthesis capability enables the device to meet the frequency and feature requirements for multiservice switch applications. The AD9551 precisely generates a wide range of standard frequencies when using any one of those same standard frequencies as a timing base reference. The primary challenge of this function is the precise generation of the desired output frequency because even a slight output frequency error can cause problems for downstream clocking circuits in the form of bit or cycle slips. The requirement for exact frequency translation in such applications necessitates the use of a frac-tional-N-based PLL architecture with variable modulus.

**Applications**

- .

- Multiservice switches

- .

- Multiservice routers

- .

- Exact network clock frequency translation

- .

- General-purpose frequency translation

### Features and Benefits

- .

- Translation between any two standard network rates

- .

- Dual reference inputs and dual clock outputs

- .

- Pin programmable for standard network rate translation

- .

- SPI programmable for arbitrary rational rate translation

- .

- Output frequencies from 10 MHz to 900 MHz

- .

- Input frequencies from 19.44 MHz to 806 MHz

|

- .

- On-chip VCO

- .

- Meets OC-192 high band jitter generation requirement

- .

- Supports standard forward error correction FEC rates

- .

- Supports holdover operation

- .

- Supports hitless switchover and phase build-out even with unequal reference frequencies

- .

- SPI-compatible 3-wire programming interface

---|---