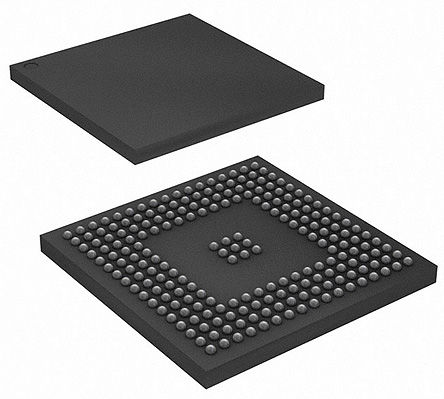

AT91SAM9G25-CU

数据手册.pdfSMART SAM9G ARM® 9 微处理器基于 ARM926™ 的 Atmel® SMART SAM9G 嵌入式微处理器单元 MPU 是高性能数据速度处理器,带扩展外围设备,用于连接和用户界面。### ARM 微控制器,Atmel

The is a SMART 400MHz 32-bit Embedded Microprocessor Unit based on ARM926EJ-S processor. The SAM9G25 interface peripherals include a camera interface that supports direct connection to the ITU-R BT. 601/656 8-bit mode compliant sensors and up to 12-bit grayscale sensors. Communication peripherals include a soft modem supporting exclusively the conexant SmartDAA line driver, HS 480Mbps USB host and device ports with on-chip transceivers, FS USB host, 10/100 Ethernet MAC, two HS SDCard/SDIO/MMC interfaces, USARTs, SPIs, I²S, multiple TWIs and 10-bit ADC. The multi-layer bus matrix is linked to 2 x 8 DMA channels as well as DMAs dedicated to the communication and interface peripherals, ensuring uninterrupted data transfers with minimal processor overhead. The External Bus Interface incorporates controllers for 4-bank and 8-bank DDR2/LPDDR, SDRAM/LPSDRAM, static memories, as well as specific circuitry for MLC/SLC NAND flash with integrated ECC up to 24 -bit.

- .

- ARM926EJ-S ARM Thumb processor running at up to 400MHz at 1.0V ±10%

- .

- 16kB Data cache, 16kB Instruction cache, memory management unit

- .

- Power-on reset cells, reset controller, shutdown controller, periodic interval timer, WDT and RTC

- .

- Boot mode select option, remap command

- .

- Internal low power 32kHz RC and fast 12MHz RC oscillators

- .

- Selectable 32768Hz low-power oscillator and 12MHz oscillator

- .

- One PLL for the system and one PLL at 480MHz optimized for USB high speed

- .

- Twelve 32-bit-layer AHB bus matrix for large bandwidth transfers

- .

- Dual peripheral bridge with dedicated programmable clock for best performances

- .

- Two dual port 8-channel DMA controllers DMAC

- .

- Advanced interrupt controller AIC and debug unit DBGU

- .

- Two programmable external clock signals

- .

- Shutdown controller with four 32-bit battery backup registers

- .

- Clock generator and power management controller

- .

- Very slow clock operating mode, software programmable power optimization capabilities

- .

- Four 32-bit parallel I/O controllers

- .

- 105 Programmable I/O lines multiplexed with up to three peripheral I/Os

- .

- Input change interrupt capability on each I/O line, optional Schmitt trigger input

- .

- Individually programmable open-drain, pull-up and pull-down resistor, synchronous output

- .

- ITU-R BT. 601/656 Image sensor interface ISI