单片机常用的串行总线标准

时间:2021-11-15 11:28:00

一、单片机串行扩大概述

单片机串行扩大完成要领,经常使用的串行总线规范主要有:I2C总线、串行总线SPI和通用串行总线USB等。本章将重点讲述I2C总线。

1. 经由过程公用串行规范总线完成

(1)串行核心设置装备摆设接口总线SPI

SPI(Serial Peripheral Interface)是一个同步串行接口规范,3线布局,使历时只要4条线就能与多种规范的核心设置装备摆设举行接口。它接纳全双工3线同步数据传输体式格局,多主从机布局方式。(2)通用串行总线USB

USB(Universal Serial Bus)标准是由Intel公司为主,联结几家天下闻名的计算机和通讯公司配合制定的串行接口总线规范。其特色:①连线简略,应用便利。

②传输速度从几kbps到几Mbps,适用于中低速设置装备摆设接口。

③拥有较强的纠错性能,以是可靠性高。

(3)存取(造访)总线ACCESS

ACCESS总线由DEC公司开辟,是一种双向总线,至多可把125台内部设置装备摆设接入体系。凡支撑该总线的内部设置装备摆设都拥有一种与德律风接插头近似的端口连接器,并以菊花型连贯体式格局接入设置装备摆设。2. 经由过程串行通信口UART完成

应用80C51的串行通信口UART的事情体式格局0能够完成串行I/O接口性能,在单片机与内部设置装备摆设或操纵设置装备摆设之间举行数据传输。3. 经由过程软件模仿完成

经由过程并行口线应用软件模仿要领也能够完成串行接口。但接口性能会遭到限定,以是只适用于最简略的串行接口使用。二、 I2C总线

I 2C(Inter Integrated Circuit)总线是一种串行同步通讯手艺,是Philips公司针对单片机需求而研制的,用于完成单片机串行核心扩大。I 2C总线经由过程两条线以及两组旌旗灯号的互相合营,就能完成串行数据传输。1、 I2C总线布局和旌旗灯号

I 2C总线拥有严峻的标准,具体表当初接口的电气功能,旌旗灯号时序,旌旗灯号传输的界说,总线状况配置和处置,以及总线治理划定规矩等方面。(1) I2C总线布局

I 2C总线是由串行时钟线SCL(Serial Clock Line)和串行数据线SDA(Serial DataLine)组成的双向数据传输通路,此中SCL用于传递时钟旌旗灯号,SDA用于传递数据旌旗灯号。经由过程I 2C总线组成的单片机串行体系中,挂接在总线上的单片机以及种种核心芯片和设置装备摆设等统称为器件,其体系布局如下图所示。一个I 2C总线体系同意接入多个器件,传输速度分歧也能够,以至还可所以另一个长途I 2C体系的驱动电路,从而构成两个I 2C体系的互相交代。(2)I 2C总线器件接入I 2C总线的两条线SCL和SDA都是通过上拉电阻(普通为10 kΩ)以漏极开路或集电极开路输入的方式接入I 2C总线的,器件与I 2C总线的连贯I 2C总线云云连贯发生以下硬件瓜葛:总线体系中各器件对SCL线是逻辑“与”的瓜葛,对SDA线也是逻辑“与”瓜葛。反之,关于低电平是逻辑“或”的瓜葛,即体系中任一器件输入低电平都会使与之相连的总线变低。这类瓜葛使得I2C总线拥有一大好处,即器件能够随时接入或移出,而不会对体系发生任何不良影响。另外,从图中还能够看出SCL和SDA均为双向传输线,由于各器件中都有输出和输入操纵。(3)I2C总线的状况和旌旗灯号

1)总线余暇

SCL和SDA均处于高电平状况,即为总线余暇状况。

2)占领总线和开释总线

器件若想应用总线应该先占有它,占领总线的主控器件向SCL线收回时钟旌旗灯号。数据传输完成后应该实时开释总线,即解除对总线的操纵(或占领),使其复原为余暇状况。

3)时钟旌旗灯号和数据旌旗灯号

时钟旌旗灯号出现在SCL线上,而数据旌旗灯号在SDA线上传输。数据传输以位为单元,一个时钟周期只能传输一名数据。SDA线上高电平为数据位1,低电平为数据位0。时钟旌旗灯号和数据旌旗灯号的合营瓜葛是:在时钟旌旗灯号高电平时期数据线上的电平状况必需坚持稳固,惟独在时钟信号为低电平时,才同意数据位状况产生变迁。如下图。

4)启动旌旗灯号和休止旌旗灯号

启动旌旗灯号和休止旌旗灯号只能由主控器件收回,它们所对应的是SCL的高电平与SDA的跳变。当SCL线为高电平时,主控器件在SDA线上发生一个电平负跳变,这便是启动旌旗灯号。当SCL线为高电平时,主控器件在SDA线上发生一个电平允跳变,这便是总线的休止旌旗灯号。休止旌旗灯号涌现后要隔断必定时候,能力觉得总线被开释并前往余暇状况。

平日启动旌旗灯号用S暗示,休止旌旗灯号用P暗示。

另外,在数据传输过程当中也大概涌现启动旌旗灯号,但这个启动旌旗灯号称为重复启动旌旗灯号,用Sr暗示,收回重复启动旌旗灯号是为了开端一次与后面分歧的新的数据传输。

5)应对旌旗灯号和非应对旌旗灯号

应对旌旗灯号是对字节数据传输的确认,每当一个字节数据传输完成后,应该由接受器件前往一个应对旌旗灯号应对旌旗灯号应对旌旗灯号对应于第9个时钟脉冲,SDA坚持高电平,则为应对旌旗灯号历时应对旌旗灯号以ACK暗示应对旌旗灯号以ACK(或NA暗示等候状况

- 在I2C总线赋与接受数据的器件体系进入等候状况权利等候状况只能在一个数据字节残缺接受以后举行。

2、 I2C总线数据传输体式格局基础数据传输花样

I2C总线上的数据传输举行,高位在前,低位在后,每传输一个数据字节经由过程应对旌旗灯号举行一次联结传递的字节数不受限定。其传输花样如下图所示。

(2)主发送体式格局

主发送体式格局是指主控器件向被控的从器件发送数据。主发送体式格局的数据传输花样如下图所示接受体式格局

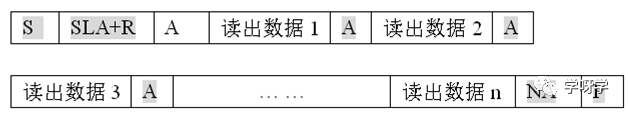

主控器件接受被控从器件发送来的数据便是接受体式格局,其数据传输花样如如下图所示。

3 、器件与器件寻址

(1)器件分类操纵瓜葛划分,器件之间存在着操纵操纵瓜葛(或主从瓜葛此中操纵感化的称为主器件(或主控器件操纵的则称为从器件(或被控器件)。

按数据的传输瓜葛划分,器件之间存在着发送与接受瓜葛此中发送数据的器件称为发送器接受数据的器件则称为接收器。

(2)器件事情体式格局

总线体系中的器件有4种事情体式格局,即主发送体式格局(该器件作为主控器件发送数据接受体式格局(该器件作为主控器件接受数据)、从发送体式格局(该器件作为被控器件发送数据)以及接受体式格局(该器件作为被控器件接受数据)。

(3)在I2C总线体系因为没有地点线可供应用地点只能经由过程串行线SDA传递。用户体贴的是器件寻址若何找到从器件。

1)器件编址

在I2C总线中,器件编址也称为器件地点。I2C总线启动后主控器件发送的第一个字节是寻址字节,以SLA+R暗示此中SLA暗示的前7位即为器件地点。I2C器件编址由“I2C 总线委员会对立调配而且遵照必定划定规矩。

如:PCF8574( I2C总线到8位并行总线转换器)

2)引脚地点

编址位中的A2A1A0、A1A0和A0暗示其对应位的编码经由过程外接电平失掉的。这几位器件编码经由过程引脚设定以是就称为引脚地点。芯片的引脚地点老是从最低位开端部署。

三、单片机8×C552的I2C总线

1、 8×C552的I2C总线接口电路 (1) I2C总线接口布局 单片机芯片8×C552是在保留原UART串行通信口的基础上此外增加了一个I2C总线接口平日本来用于串行通讯的串行口叫SIO0,而把I2C总线接口命名为SIO1。SIO1的电路布局如下图所示。 I2C总线接口基础逻辑由总线输出输入电路比拟器、串行时钟发生器、总线合作和同步逻辑以及准时操纵逻辑构成。 ① 总线输出输入电路。SCL和SDA都是双向线。SCL的双向性因为主控器件经由过程它发送时钟旌旗灯号,同时还要随时监测其电平变迁,用以肯定SDA线上旌旗灯号变迁。 ③ 总线合作和同步逻辑。I2C总线合作的仲裁与时钟同步完整依托硬件电路完成毋庸野生干涉干与。 ④ 串行时钟发生器。SCL时钟脉冲是由主控器件供应的,为此8×C552有一个可编程的串行时钟发生器方便它作为主控器件时能向总线收回时钟脉冲。而当8×C552作为被控从器件堵截时钟发生器。时钟脉冲频次抉择经由过程对总线接口电路操纵寄存器S1CON相干举行配置完成的。 8×C552芯片中没有配置公用的I2C时钟旌旗灯号和数据旌旗灯号引线,而是借用P1口的两条口线,P1.6——SCL( I2C总线时钟信号线);P1.7—— SDA( I2C总线数据信号线) (2)I2C总线公用寄存器 8×C552的I2C总线接口电路包括4个公用寄存器地点寄存器S1ADR、数据寄存器S1DAT操纵寄存器S1CON状况码寄存器S1STA。 S1ADR寄存器的内容由用户经由过程步伐写入此中最低位GC用于划定播送呼唤是不是作出呼应,GC呼应;GC=0为不予答理。 (3)I2C总线中缀 带有I2C接口的单片机芯片8×C552中,增加了一个中缀范例,即I22C总线的数据传输办事的。每当总线上一个基础操纵完成后,便在发生状况码的同时,由硬件中缀同意寄存器IE0的ESI这时候假如中缀体系开放且I22 2、 8×C552的I2C总线操纵机制 (1)I2C总线状况码 所谓状况是指一个基础操纵子程序运转后I2C总线接口中电路状况状况码则是状况的二进制编码。 为此,在8×C552的I2C总线接口电路中有状况译码电路状况码寄存器,每当一个基础操纵完结后,就由状况译码电路发生5位状况状况码保存在8位状况码寄存器占领其高5位,而将其低3位弥补,从而失掉8位状况因为低3位以是状况顺次相差8。I2C总线共有26种基础操纵于是也就有26个响应状况状况码表略。 (2)I2C总线和谈驱动步伐 I2C总线接纳应用后面操纵失掉状况经由过程中缀疏导后续操纵思绪举行数据传输。 ORG0000H STRT: LJMPMAIN 体系复位后转使用步伐 ORG002BH IICI: PUSHPSW ;I2C中缀办事步伐 PUSHS1STA PUSHHADD RET ;返回到响应的后续处置子程序 ORG00A0H INITS1: MOVPSW,#18H 抉择寄存器组 MOVR1,#MTD ;发送数据缓冲区首址 MOVR0,#MRD 接受数据缓冲区首址 MOVBACKUP,NUMBYT ;字节数 POPPSW 复原步伐状态字 RETI 3、 由8×C552组成的单主I2C总线体系 单主I2C总线体系的数据传递只有主发送接受两种体式格局。在I2C总线全数26个状况体式格局的数据发送接受操纵触及10个,即08H、10H、18H、20H、28H、30H、40H、48H、50H和58H。 存储器芯片,只能接纳主发送体式格局。 传输步伐设想 MAIN: MTD EQU 30H MRD EQU 38H SRD EQU 40H STD EQU 48H HAAD EQU 50H SLA EQU 51H NUMBYT EQU 52H BACKUP EQU 53H MOVS1ADR, #××H ;8×C552的器件地点写入 SETBP1.6 ;口线锁存器置1,供I2C总线应用 SETBP1.7 MOVHAAD, #01H ;配套步伐地点高8位 ORLIE0, #0A0H ;开放I2C总线中缀体系 CLR0BDH 配置为低优先级 MOVS1CON, #0C5H ;I2C总线接口配置时钟频次 MOVNUMBYT, #08H 传递数据字节数 MOVSLA, #0A0H ;寻址字节SLA+W SETBSTA ;启动I2C总线操纵 IICI: PUSHPSW PUSHS1STA PUSHHADD RET (2)数据传递进程解释 1)SI08(启动旌旗灯号失常收回预备发送SLA+R接受应对旌旗灯号) 2)SI18收回SLA+W后收到应对旌旗灯号预备发第一个数据字节) 3)SI28(发送一个数据字节后收到应对旌旗灯号预备连续发送数据字节休止旌旗灯号) 在SI28子程序中,字节数效果不为0,转向上级子程序NOLD1经由过程NOLD1发送下一个数据。接收到应对旌旗灯号失掉状况仍是28H,从而使数据发送得以屡次重复。

四、单片机8×C552的串行扩大

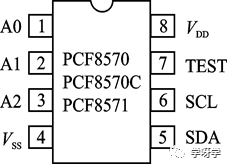

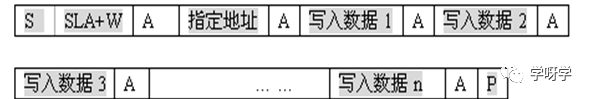

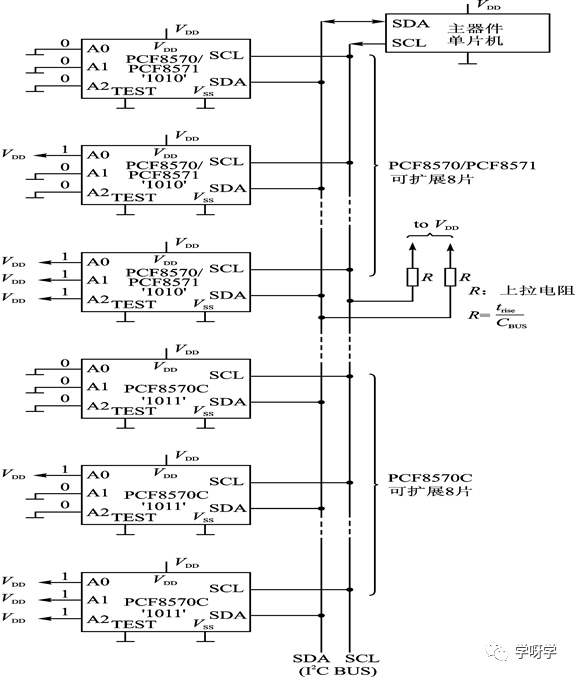

1、 经由过程I2C总线扩大串行数据存储器 (1)PCF8571/8570/8570C芯片概述 PCF8571/8570/8570C拥有I2C总线接口的低功耗CMOS动态RAM芯片此中PCF8571容量为128字节,器件编码是1010;PCF8570为256字节,器件编码也是1010;PCF8570C为256字节,器件编码是1011。引脚以下:

-

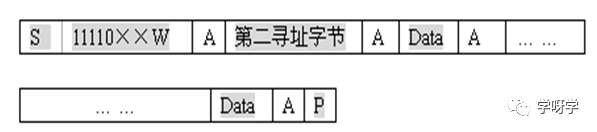

指定地点写

-

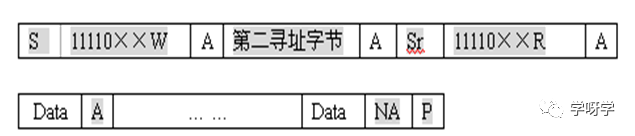

指定地点读

-

现行地点读

(3) 串行数据存储器扩大连贯因为PCF8571/8570/8570C存储芯片的容量较小以是扩大存储容量较大需求接入多个芯片。下图便是一个多片数据存储器扩大体系。

I2C总线体系中的多片数据存储器扩大

2、 I2C总线进展 图示是3个地点的芯片。

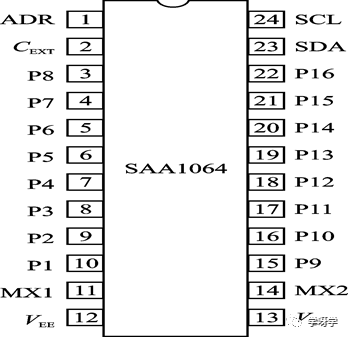

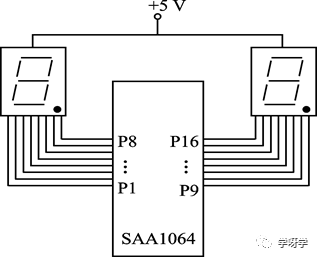

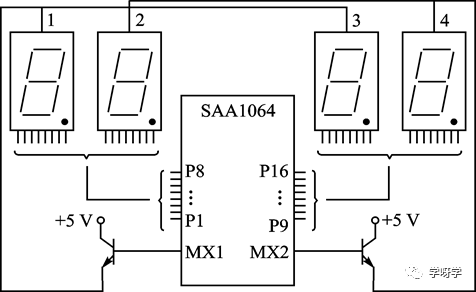

(1)LED驱动芯片SAA1064 SAA1064是I2C总线体系比拟典范公用LED驱动芯片,器件编址为0111,共有2组8位段码驱动输入接纳24引脚双列直插式封装,如下图所示。

(2)SAA1064的接口连贯操纵

(2)SAA1064的接口连贯操纵

SAA1064静态表现体式格局接口连贯

(3)SAA1064特色 与并行体式格局LED表现接口相比,SAA1064除能驱动LED表现外,还具有一些操纵性能操纵性能操纵界说花样暗示以下:

五、单片机80C51的串行扩大

1 经由过程UART举行串行步伐存储器扩大

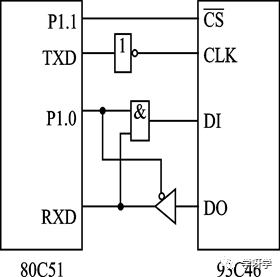

串行步伐存储器扩大平日应用串行E2PROM电擦除可编程只读存储器芯片这种芯片中,有一些能够经由过程UART举行串行存储器扩大比方93C46。该芯片的引脚罗列如下图经由过程80C51的串行口UART举行串行存储器扩大连贯其实不庞杂比方,93C46连贯如下图 。

93C46芯片引脚罗列

的串行存储器扩大连贯

2、 串行接口的软件模仿

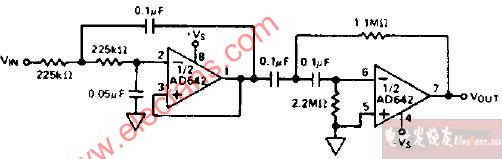

串行接口性能能够经由过程软件模仿完成,即在并行口线上经由过程软件驱动完成串行数据传输,在一些简略的没有串行接口体系中常应用这类要领。现以80C51与PCF8582的串行接口解释I2C总线接口的软件模仿要领。

以80C51的P3.4和P3.5分手作为I2C的串行时钟线SCL和串行数据线SDA,其电路连贯如下图所示。

在80C51芯片因为P3口线内有上拉电阻以是不消外接上拉电阻。在PCF8582芯片上,A2、A1、A0接地,即引脚地点为000。

为启动I2C总线,应先把SCL和SDA线都置高,经一段时候耽误后,再把SDA线变低如下各指令序列挪用或跳转耽误子程序DELAY,只是为了解释在该处需求有时间耽误。

SCL EQU 0B4H

SDA EQU 0B5H

SETB SCL

NOP

NOP

SETB SDA

ACALLDELAY

CLR SDA

PCF8582拥有I2C总线接口电路,能检测到总线上的启动旌旗灯号,并随后进入事情状况接受80C51发送来的寻址字节。

在I2C总线中,数据传递是高位在前低位在后以是应用轮回左移指令RLC先把数据位移入标记位C,再用传递指令发送进来。2条指令以下:

RLC A

MOV SDA,C

PCF8582每接收到一个字节数据应该前往应对旌旗灯号,为了驱逐PCF8582应对旌旗灯号,80C51模仿步伐开释SDA线,使其变成高电平。同时也应将SCL线先变高再变低发生第9个时钟脉冲。指令序列以下:

SETB SDA

ACALL DELAY

SETB SCL

ACALL DELAY

CLR SCL

如果是读PCF8582操纵,80C51每接收到一个数据字节后,向PCF8582发送应对旌旗灯号,即把SDA变低发生第9个时钟脉冲。为此应用以下指令序列:

CLR SDA

ACALL DELAY

SETB SCL

ACALL DELAY

CLR SCL休止旌旗灯号应该由80C51收回,指令序列以下:

CLR SDA

NOP

NOP

SETB SCL

ACALL DELAY

SETB SDA

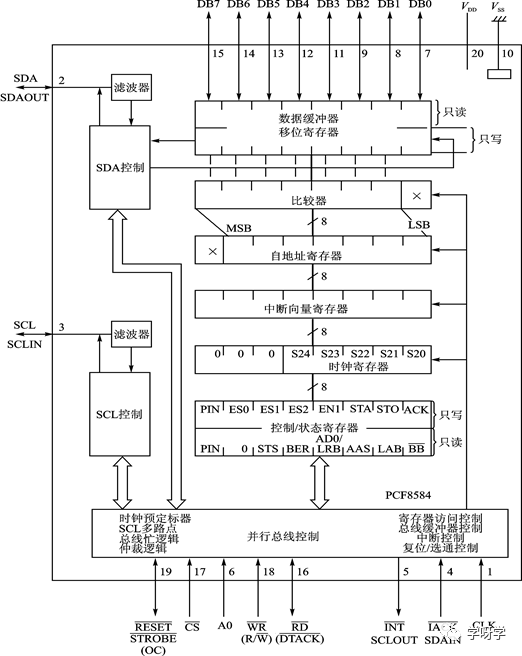

3、 I2C总线接口芯片PCF8584关于像80C51如许没有I2C总线接口的单片机,可借用I2C总线接口芯片完成I2C总线操纵。一个比拟典范的I2C总线接口芯片是PCF8584基础性能是实现从并行总线到I2C总线的转换以是该芯片也被称为并行总线——I2C总线转接器。

(1)PCF8584的逻辑布局

由PCF8584接口的单片机能在I2C总线体系中作为主控器件认为它接口的PCF8584芯片硬件布局比拟庞杂。其逻辑布局如下图所示。

并行总线与I2C总线之间的转换经由过程数据寄存器完成的。数据寄存器是数据缓冲器和移位寄存器的综合,它一方面经由过程数据缓冲器与并行总线连贯另外一方面经由过程移位寄存器与I2C总线相连二者共用一个地点以是合称为数据寄存器。

当PCF8584接口芯片要向I2C总线发送数据时,并行数据间接写入串行移位寄存器而后经由过程移位奉上SDA接受数据时,串行数据从SDA线移入移位寄存器应对旌旗灯号涌现时辰,数据从移位寄存器复制到数据缓冲器而后经由过程并行总线读入CPU上面分手先容操纵寄存器状况寄存器地点寄存器此中操纵寄存器状况寄存器因共用一个地点可写操纵状况寄存器。

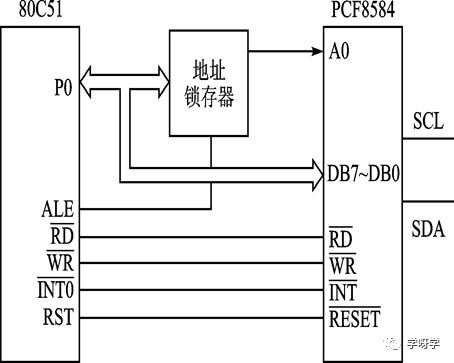

,用于寄放本芯片的器件编码经由过程PCF8584将80C51接入I<sup>2</sup>C总线 </p> <p> PCF8584首要接口性能是将单片机接入I<sup>2</sup>C总线体系,它与80C51连贯如下图所示。 </p> <p style=)

80C51与PCF8584接口连贯