FPGA小白学习如何实现一个RISC-V处理器

时间:2021-11-30 17:28:00

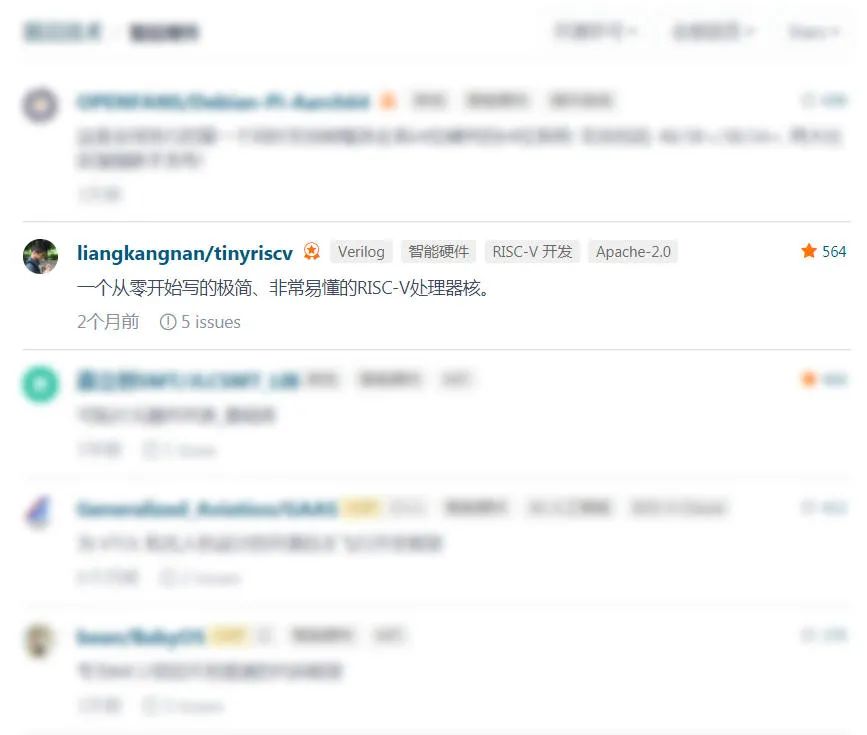

比来两年,RISC-V这个词开端频仍的出现在,从、、、再到、沁恒CH32V103等等,国内外出现出了一大批RISC-V处理器。本日分享一名大佬从零开端写的极简、异常易懂的RISC-V处理器核,从一个FPGA小白的角度,来进修若何完成一个RISC-V处理器。

比来两年,RISC-V这个词开端频仍的出现在,从、、、再到、沁恒CH32V103等等,国内外出现出了一大批RISC-V处理器。本日分享一名大佬从零开端写的极简、异常易懂的RISC-V处理器核,从一个FPGA小白的角度,来进修若何完成一个RISC-V处理器。 开源地点

该项目标Gitee开源地点: https://gitee.com/liangkangnan/tinyriscv

(长按前去项目地点)

这个项目是Gitee码云智能硬件板块Star排名第二的项目。 该项目标作者是一位FPGA小白,为了对RISC-V从CPU完成到使用级步伐开辟有一个周全的懂得,从零开端自学FPGA和Verilog HDL,终究用简略易懂的体式格局写了一个RISC-V处理器,并开源进去,因而tinyriscv在2019年12月诞生了。tinyriscv细致的开辟条记,能够到项目作者的小我私家博客检察,还在继续更新中:

该项目标作者是一位FPGA小白,为了对RISC-V从CPU完成到使用级步伐开辟有一个周全的懂得,从零开端自学FPGA和Verilog HDL,终究用简略易懂的体式格局写了一个RISC-V处理器,并开源进去,因而tinyriscv在2019年12月诞生了。tinyriscv细致的开辟条记,能够到项目作者的小我私家博客检察,还在继续更新中:https://liangkangnan.gitee.io/2020/04/29/%E4%BB%8E%E9%9B%B6%E5%BC%80%E5%A7%8B%E5%86%99RISC-V%E5%A4%84%E7%90%86%E5%99%A8/

tinyriscv的特色

本项目完成的是一个单核32位的小型RISC-V处理器核(tinyriscv),接纳verilog言语编写。设想目的是对标ARM Cortex-M3系列处理器。 tinyriscv有如下特色:- 支撑RV32IM指令集,经由过程RISC-V指令兼容性测试;

- 接纳三级流水线,即取指,译码,施行;

- 能够运转C言语步伐;

- 支撑JTAG,能够经由过程openocd读写内存(在线更新步伐);

- 支撑中缀;

- 支撑总线;

- 支撑FreeRTOS;

- 支撑经由过程串口更新步伐;

- 轻易移植到任何FPGA平台(假如资本足够的话);

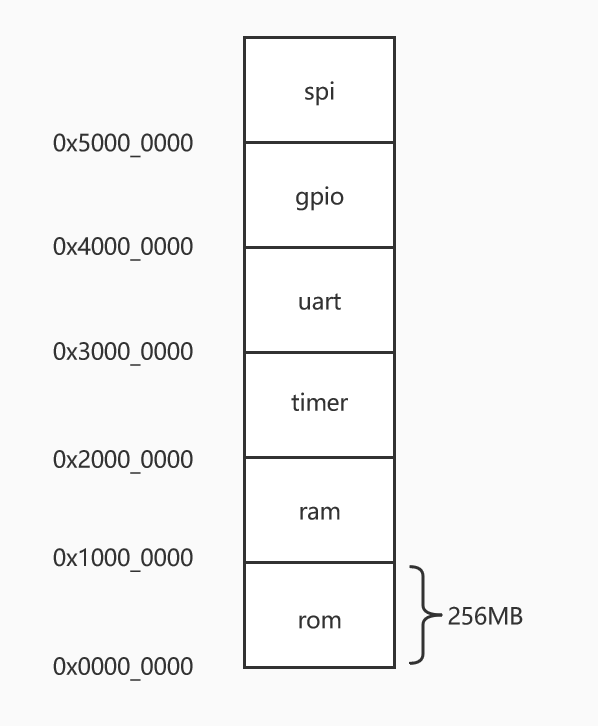

tinyriscv今朝外挂了6个外设,每一个外设的空间巨细为256MB,地点空间调配如下图所示:

tinyriscv今朝外挂了6个外设,每一个外设的空间巨细为256MB,地点空间调配如下图所示:

CoreMark功能测试

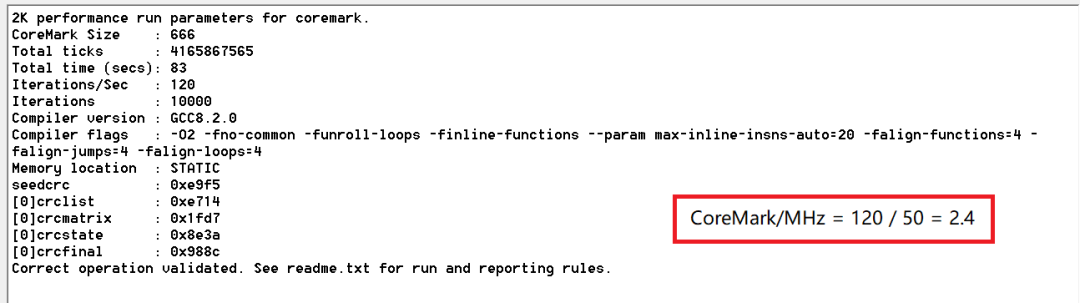

今朝tinyriscv在Xilinx Artix-7 35T FPGA平台(时钟50MHz)上运转CoreMark跑分步伐的效果如下图所示: 可知,tinyriscv问题为2.4比照其余MCU效果如下图所示:

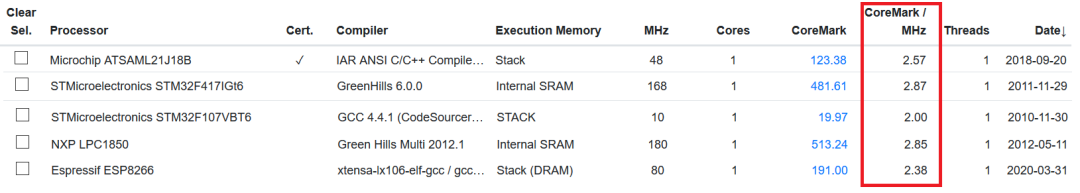

可知,tinyriscv问题为2.4比照其余MCU效果如下图所示:  更多MCU效果能够到coremark官网( www.eembc.org/coremark/scores.php

更多MCU效果能够到coremark官网( www.eembc.org/coremark/scores.php PC若何举行仿真运转

FPGA代码能够应用举行仿真和编译,波形检察对象应用支撑Windows、Linux和Mac平台步伐编译应用的是开源的gnu-mcu-eclipse-riscv-none-gcc-8.2.0-2.2-20190521-0004-win64编译对象链,还需要装置make和Python3对象。 开发板完成

作者应用的是Xilinx Artix-7 35T FPGA平台开辟环境vivado 2018.1只需FPGA资本足够,理论上能够移植到任何的FPGA平台。 总结

(长按前去项目地点)